# Service Manual

ORDER NO. ARP3051

PROJECTION MONITOR RECEIVER

# PRO-610HD PRO-510HD SD-582HD5 SD-532HD5

#### THIS MANUAL IS APPLICABLE TO THE FOLLOWING MODEL(S) AND TYPE(S).

| Туре    | Model     |           | Power Requirement | Remarks   |        |         |

|---------|-----------|-----------|-------------------|-----------|--------|---------|

| Туре    | PRO-610HD | PRO-510HD | SD-582HD5         | SD-532HD5 |        | Remarks |

| KUXC/CA | 0         | 0         | 0                 | 0         | AC120V |         |

| KBXC    |           |           |                   | 0         | AC120V |         |

## • This service manual should be used together with the following manual(s):

| Model No. | Order No. | Remarks |

|-----------|-----------|---------|

| PRO-610HD | ARP3047   |         |

## **CONTENTS**

| 6. ADJUSTMENT          | 195   | 7.2 IC                              | 228 |

|------------------------|-------|-------------------------------------|-----|

| 7. GENERAL INFORMATION | 219   | 7.3 EXPLANATION                     | 254 |

| 7.1 DIAGNOSIS          | 219 8 | PANEL FACILITIES AND SPECIFICATIONS |     |

| 7.1.1 DIAGNOSIS METHOD | 219   |                                     | 266 |

| 7.1.2 DISASSEMBLY      | 224   |                                     |     |

| 7 1 3 WIRING DIAGRAM   | 226   |                                     |     |

PIONEER CORPORATION 4-1, Meguro 1-Chome, Meguro-ku, Tokyo 153-8654, Japan PIONEER ELECTRONICS SERVICE, INC. P.O. Box 1760, Long Beach, CA 90801-1760, U.S.A. PIONEER ELECTRONIC (EUROPE) N.V. Haven 1087, Keetberglaan 1, 9120 Melsele, Belgium PIONEER ELECTRONICS ASIACENTRE PTE. LTD. 253 Alexandra Road, #04-01, Singapore 159936 © PIONEER CORPORATION 1999

# 6. ADJUSTMENT

#### **6.1 INTRODUCTION**

#### • IMPORTANT

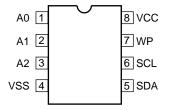

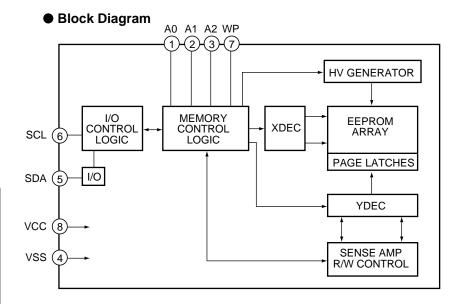

When replacement of the following assemblies are required during repairs, be sure to replace the EEPROMs with the mounted ones in order to retain the adjustment data of the unit and to facilitate adjustment after the replacement of the assemblies.

| Name of Assy       | EEPROM               | Main Contents of Memory                                      |

|--------------------|----------------------|--------------------------------------------------------------|

| SIGNAL Assy        | IC2454 [24LC32(I)P]  | Adjustment data, such as W/B and color data, in FACTORY mode |

|                    |                      | User data set on the MENU                                    |

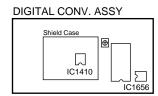

| DIGITAL CONV. Assy | IC1410 [24LC128P]    | Convergence adjustment data                                  |

|                    | IC1656 [24LC08B(I)P] | Convergence offset data                                      |

#### Notes:

- Even if the EEPROMs are replaced, adjustment may be necessary, depending on the part or assembly to be replaced. For details, see page 197.

- Even if the EEPROMs are replaced, if the EEPROMs are damaged or if their data have been changed from the adjustment data, the status before the failure will not be restored. Check the status of the unit after replacement of the EEPROMs, and readjust if necessary.

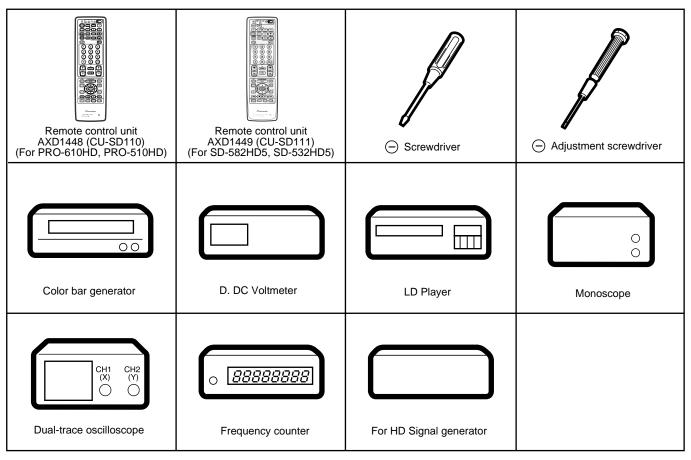

#### **6.2 JIGS AND MEASURING INSTRUMENTS**

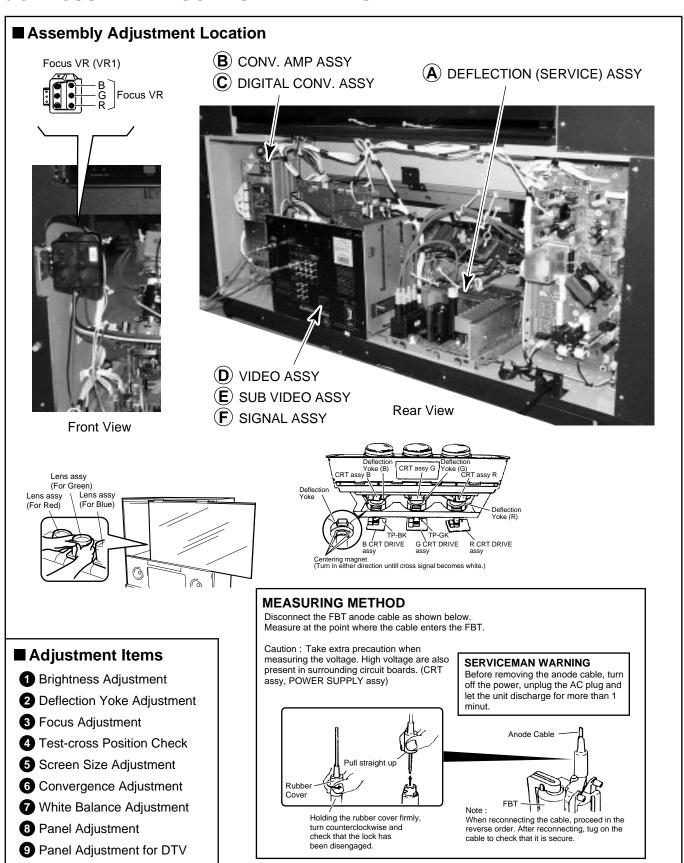

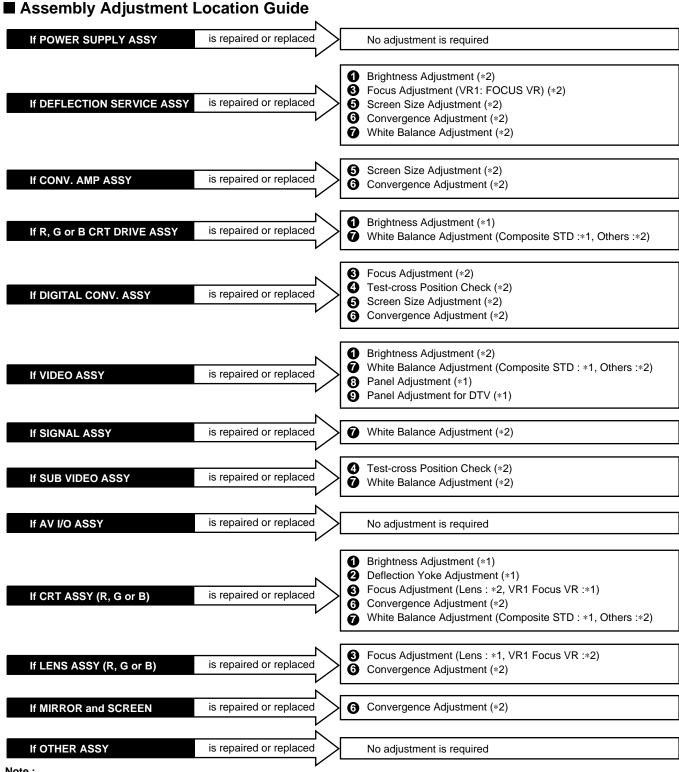

#### **6.3 ADJUSTMENT LOCATION AND ITEMS**

#### Note:

- \*1: Readjustment necessary

- \*2: Turn on the power and confirm the screen. When adjustment deviates, it is readjusted if necessory.

- When the EEPROMs are replaced, check the status of the unit.

- If any IC of the EEPROM is damaged, readjustment of all the items is necessary.

- The necessary adjustment items differ, depending on the assembly or optical part replaced. Check and readjust the adjustment items corresponding to the replaced assembly or part, following adjustment procedures 1 to 9. **Example:** When the DIGITAL CONV. Assy is replaced, perform the following:

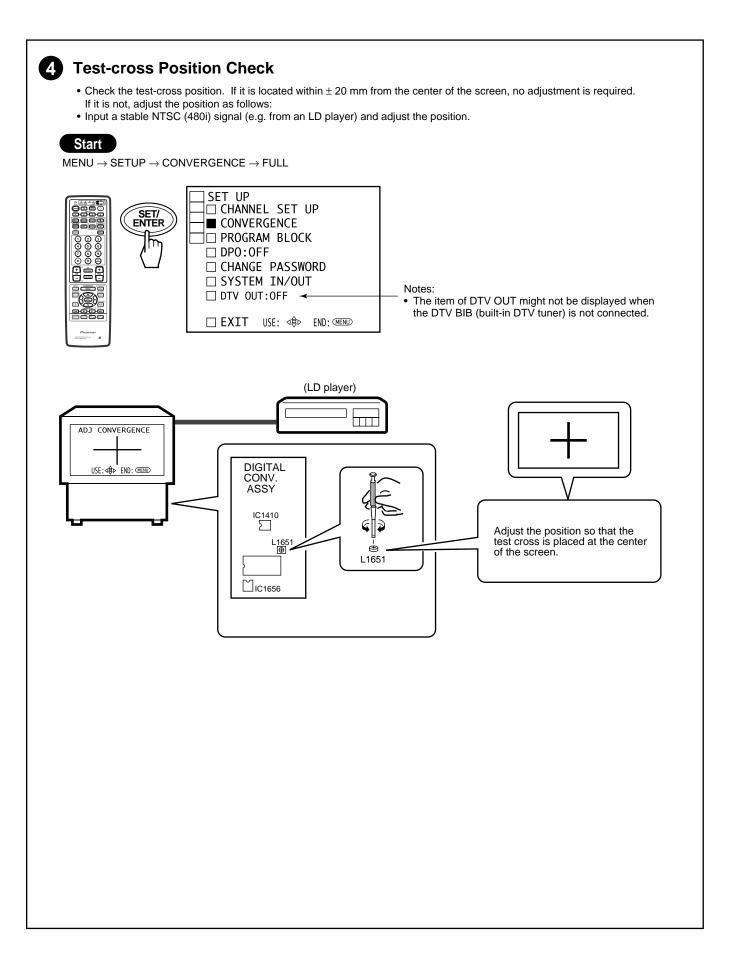

- 3. Focus check/adjustment → 4. Test-cross position check/adjustment → 5. Screen size check/adjustment → 6. Convergence check/adjustment

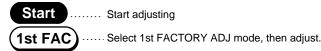

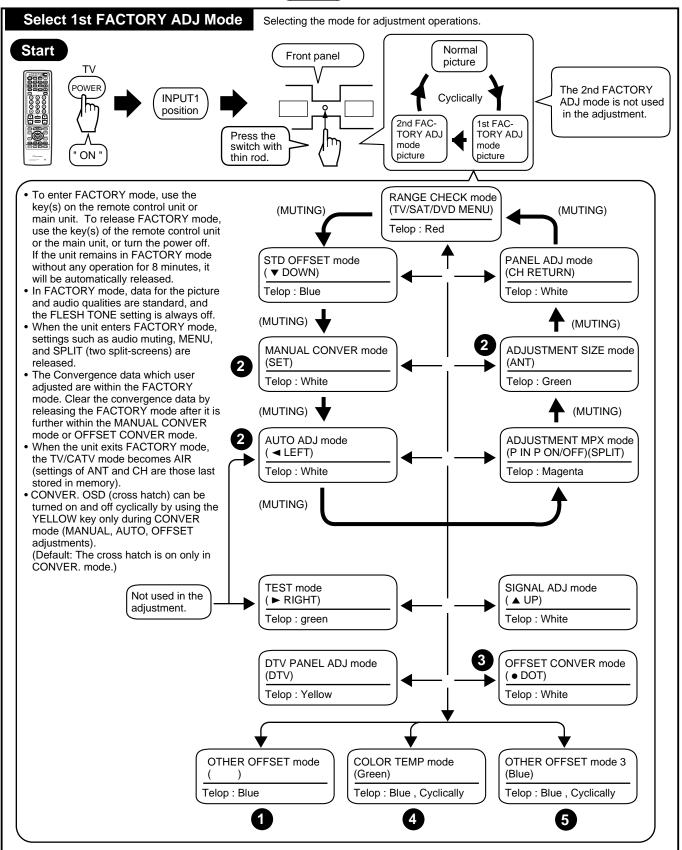

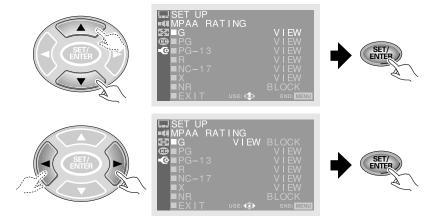

#### 6.4 FACTORY ADJ MODE

■ Factory Adjustment Mode

1 OTHER OFFSET mode

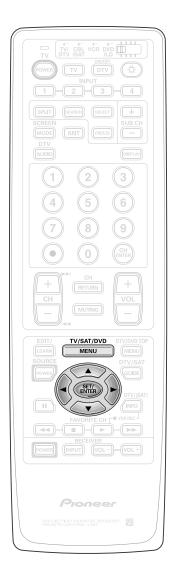

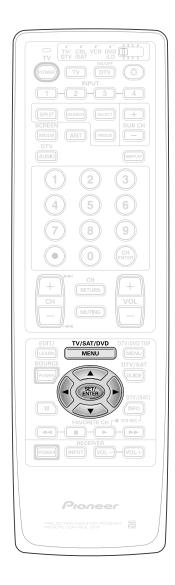

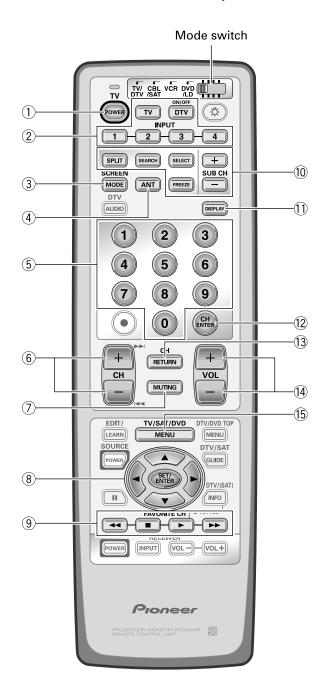

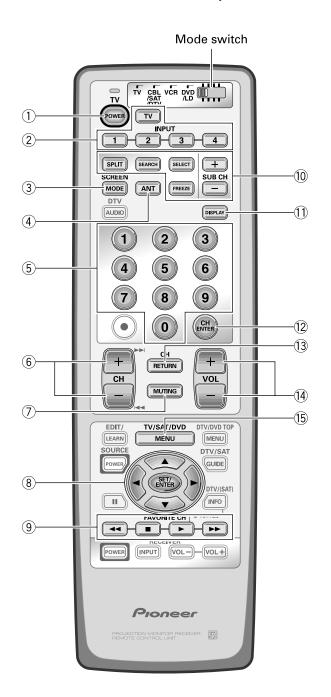

To enter the OFFSET mode of each picture quality, use the following keys and codes of the remote control unit:

|   |                                   | Key(s) on the Remote<br>Control Unit |

|---|-----------------------------------|--------------------------------------|

| Α | STD OFFSET MODE                   | DOWN                                 |

| С | COMP (15 kHz) OFFSET MODE         | P in P CH-, SUB CH-                  |

| D | COMP (31 kHz, 33 kHz) OFFSET MODE | P in P CH+, SUB CH+                  |

| В | TV OFFSET MODE                    | RED                                  |

| V | COLOR TEMP B&W for STD            | DTV MENU                             |

| L | COLOR TEMP FILM for STD & GAME    | INFO                                 |

| Т | RGB OFFSET MODE                   | CH ENTER                             |

2 The screen size modes change cyclically with each press of the SCREEN key as follows:

Note: The initial mode is always FULL.

3 The OFFSET CONVER. modes change cyclically with each press of the DOT key as follows:

```

\blacksquare ① OFFSET CONVER. MODE 1 \longrightarrow ② OFFSET CONVER. MODE 2 \longrightarrow ③ OFFSET CONVER. MODE 3 \longrightarrow

```

Note: The initial mode is always OFFSET CONVER. MODE 1.

The offset data of the picture quality in COLOR TEMP mode change cyclically with each press of the GREEN key as follows:

```

TOLOR TEMP NEWS

(2) K COLOR TEMP LIVE

(3) M COLOR TEMP FILM for MOVIE

(4) X COLOR TEMP B&W for MOVIE

(5) β COLOR TEMP NEWS for R, G, B

(6) γ COLOR TEMP LIVE for R, G, B

(7) Y COLOR TEMP FILM for R, G, B

(8) Z COLOR TEMP B&W for R, G, B

```

Note: The initial mode is always COLOR TEMP NEWS when the GREEN key is pressed.

5 The offset data of picture quality change cyclically with each press of the BLUE key as follows:

```

↑ ① E MOVIE OFFSET MODE → ② F GAME OFFSET MODE —

```

Note :The initial mode is always (1) when the BLUE key is pressed.

#### **6.5 ADJUSTMENT**

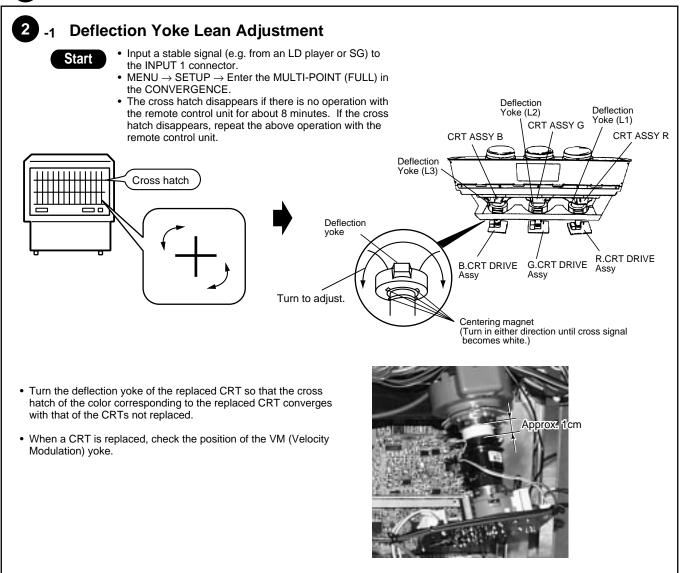

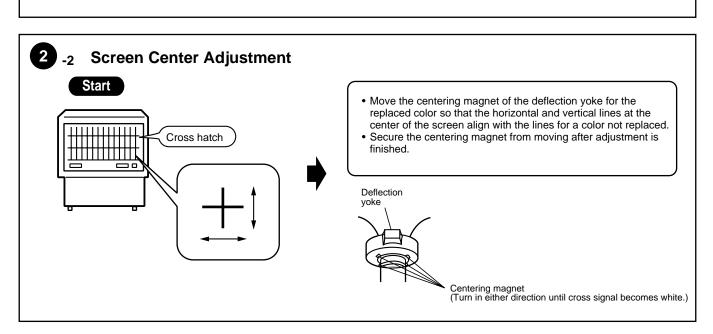

# 2 Deflection Yoke Adjustment

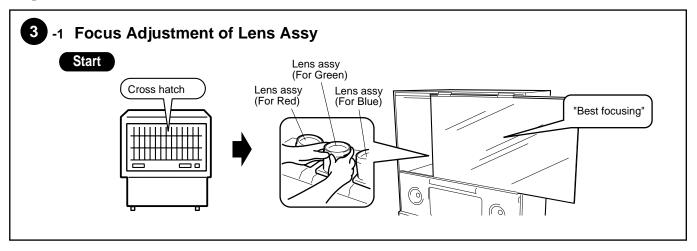

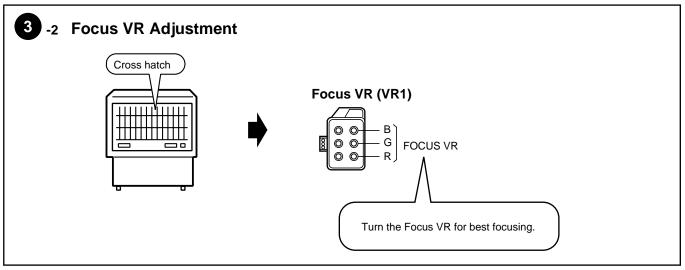

# 3 Focus Adjustment

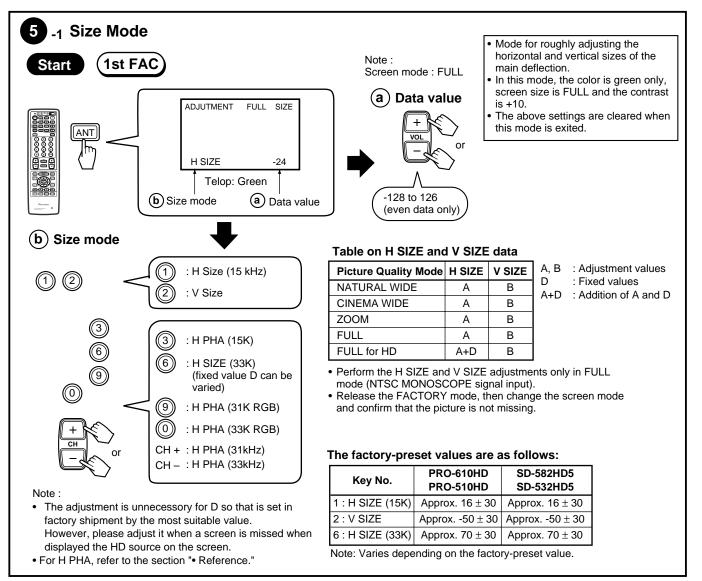

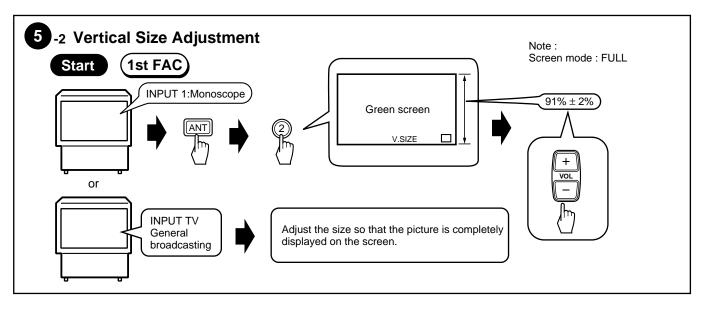

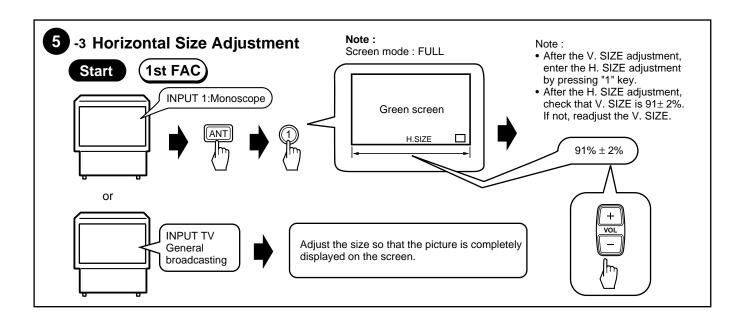

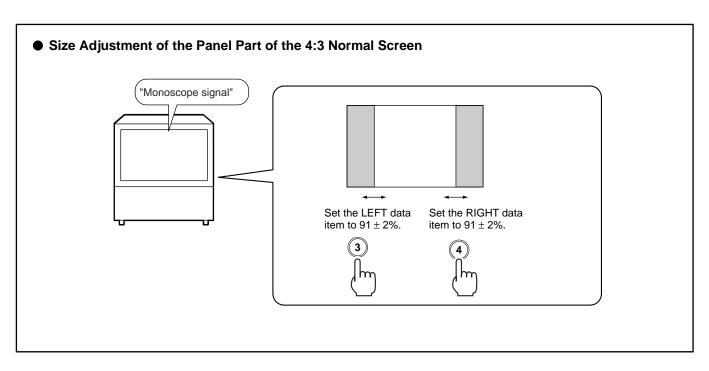

# 5 Screen Size Adjustment

Check if both vertical and horizontal sizes are within 91% ±2%. If they are not, perform the size adjustment as follows:

#### Reference

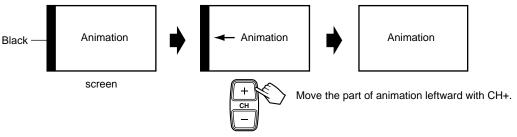

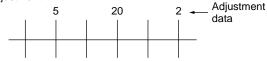

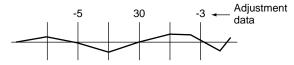

The H PHASE adjustment is required if the left or right part of the screen becomes black, as illustrated below, depending on the format of the input signal (Ex. component 31.5 kHz, RGB 33K etc.).

#### Ex. Component 31K

#### • About H. PHASE

In principle, adjustment of the data for the H. PHASE is not required. Check whether the H. PHASE data are the factory-preset values, as indicated below:

| Key No.             | PRO-610HD<br>PRO-510HD | SD-582HD5<br>SD-532HD5 |  |  |

|---------------------|------------------------|------------------------|--|--|

| 3 : H PHA (15K)     | 80                     | 80                     |  |  |

| CH+: H PHA (31K)    | 36                     | 40                     |  |  |

| CH-: H PHA (33K)    | -14                    | -8                     |  |  |

| 9 : H PHA (31K RGB) | 26                     | 30                     |  |  |

| 0 : H PHA (33K RGB) | -26                    | -20                    |  |  |

15K: CONPOSITE, S COMPONENT (480i)

31K: COMPONENT (480P) 33K: COMPONENT (1080i)

The screen moves to the right or the left if the above data are in variance. (See the above figures.)

#### Note:

H PHASE is set in factory shipment by the most suitable value. But, there is the case that screen is missed as an upper figure occurs by the signal format of other apparatus to be connected to.

A screen can be improved as the following by the readjustment. However, attention is necessory because in convenience may occur when connected to another apparatus.

## **6** CONVERGENCE ADJUSTMENT

#### 1. Procedures

- When replacinf the DIGITAL CONV. Assy, replace the EEPROM of new DIGITAL CONV. Assy with the EEPROM of old DIGITAL CONV. Assy.

- 2. Check the initial data for the convergence adjustment.

- 3. Perform the coarse adjustment for the green to roughly correct distortion of the green.

- 4. Fine-adjust the green to eliminate any distortion. The green becomes the standard for the red and the blue.

- If necessary, repeat steps 3 and 4. Green adjustment is completed.

- 5. Perform the coarse adjustment for the red by roughly converging the red with the green.

- 6. Fine-adjust the red until the red is completely converging with the green.

- If necessary, repeat steps 5 and 6. Red adjustment is completed.

- 7. Perform the coarse adjustment for the blue by roughly converging the blue with the green.

- 8. Fine-adjust the blue until the blue is completely converging with the green.

- If necessary, repeat steps 7 and 8. Blue adjustment is completed.

- Display the green, red, and blue colors at the same time to check the convergence. Readjust the convergence if necessary.

#### 2. Prior to Adjustment

There are five screen modes, and convergence adjustment is required for each mode. For adjustment, input the following video signal:

Table 1 Input signal

| Screen mode                | Input signal          |

|----------------------------|-----------------------|

| 1. FULL (FULL, 4:3 NORMAL) |                       |

| 2. ZOOM (ZOOM)             | NTSC (480i) signal    |

| 3 CINEMA (CINEMA WIDE)     |                       |

| 4. NATURAL (NATURAL WIDE)  |                       |

| 5. FULL for HD (HD/DTV)    | HD/DTV (1080i) signal |

NTSC: Stable signal source, such as an SG or an LD/DVD player

HD: Stable signal source, such as an HD SG or a DTV tuner (SH-D09, etc.) Only PRO-610HD5/510HD5 can use the SH-D09.

When CRTs are replaced or when the deflection yoke is moved, perform the deflection yoke adjustment, horizontal and vertical size adjustments, and centering magnet adjustments before the convergence adjustment. (See Pages 201, 204 and 205)

# 3. Convergence Adjustment

# 3.1 Replacement of the EEPROMs inside the DIGITAL CONV. Assy

IC1410 24LC128P IC1656 24LC08B (I) P

The data stored in the EEPROMs are as follows: IC1410

OFFSET CONVER. MODE 1 (DFH, DFV)

OFFSET CONVER. MODE 3

Factory-preset values for convergence

User-adjusted values for convergence (CENTER, MULTI-POINT)

IC1656

OFFSET CONVER. MODE 1 (HDP) OFFSET CONVER. MODE 2

#### 3.2 Confirmation of convergence data

The convergence coarse adjustment modes change cyclically, as shown below, with each press of the DOT key in FACTORY mode:

#### Convergence coarse adjustment

DOT key (pressed once) : OFFSET CONVER. MODE 1

DOT key (pressed twice) : OFFSET CONVER. MODE 2

DOT key (pressed three times) : OFFSET CONVER. MODE 3

Cyclical change

Check whether the data of MODE 1 and MODE 2 are as shown in Table 2.

The cross-hatch signal is generated inside the unit, and is automatically displayed in OFFSET CONVER. mode and MANUAL CONVERGENCE mode. You can turn on and off the cross-hatch signal with the YELLOW key.

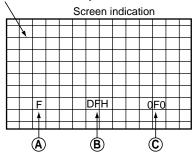

Screen mode:

F : FULL Z : ZOOM C : CINEMA

N: NATURAL H: FULL for HD

The Screen modes change cyclically with each press of the SCREEN mode key.

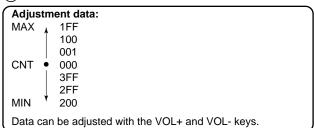

**(B)**

Adjustment items can be selected with the numeric keys. See Table 2.

**(C)**

**Table 2 OFFSET CONVER DATA**

| OFFSET CONVER MODE 1 |            |             |           |             |              |              |  |

|----------------------|------------|-------------|-----------|-------------|--------------|--------------|--|

| Numeric              | Adjustment | Screen Mode |           |             |              |              |  |

| Key                  | Item       | F<br>FULL   | Z<br>ZOOM | C<br>CINEMA | N<br>NATURAL | H<br>HD FULL |  |

| 1                    | DFH        | 0F0         | 0D0       | 0D0         | 0D0          | 100          |  |

| 2                    | DFV        | 070         | 070       | 070         | 070          | 070          |  |

| 3                    | HDP        | 010         | 010       | 010         | 010          | 010          |  |

| OFFSE   | CONVER     | MODE        | 2    |        |         |         |  |  |

|---------|------------|-------------|------|--------|---------|---------|--|--|

| Numeric | Adjustment | Screen Mode |      |        |         |         |  |  |

| Key     | Item       | F           | Z    | С      | N       | Н       |  |  |

|         |            | FULL        | ZOOM | CINEMA | NATURAL | HD FULL |  |  |

| 1       | HFP        | 0CC         | 0CC  | 0CC    | 0CC     | 0D0     |  |  |

| 2       | HCP        | 00F         | 00F  | 00F    | 00F     | 015     |  |  |

| 3       | HTP        | 047         | 047  | 047    | 047     | 044     |  |  |

| 4       | HHD        | 0EE         | 0EE  | 0EE    | 0EE     | 0E9     |  |  |

| 5       | HPW        | 00C         | 00C  | 00C    | 00C     | 00F     |  |  |

| 6       | V1C        | 01F         | 029  | 025    | 022     | 01D     |  |  |

| 7       | V1S        | 000         | 000  | 000    | 000     | 000     |  |  |

| 8       | VFP        | 01D         | 02D  | 013    | 033     | 065     |  |  |

The above offset convergence values are common to the PRO-610 HD/510HD and SD-582HD5/532HD5.

If the offset convergence values are as indicated in Table 2, proceed to 3.3. If the values are not the same, adjust the values with the numeric keys and VOL +/- keys.

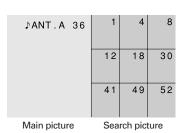

#### Example:

To check HDP in ZOOM mode of OFFSET CONVER. MODE 1

- ① Enter the FACTORY mode.

- ② Enter the OFFSET CONVER. MODE 1 by pressing the DOT key once.

- ③ Enter the ZOOM screen mode by pressing the SCREEN mode key once. (When the unit enters FACTORY mode, the screen mode automatically becomes FULL.)

- ④ Check the indication on the screen by pressing the numeric key 3.

Indication at the bottom of the screen: Z HDP 010 If the adjustment value is 010, adjustment is not required. If the adjustment value is other than 010, adjust with the VOL + or VOL- key so that the value becomes 010.

#### 3.3 Coarse Adjustment of the Green

(Proceed with 3.3 and afterwards when the DIGITAL CONV. Assy is not replaced.)

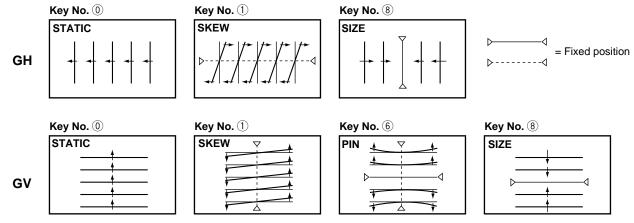

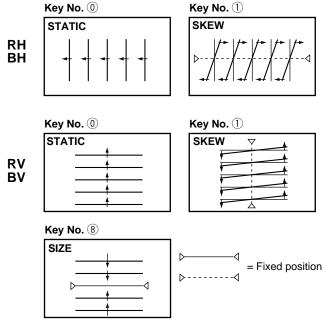

Select adjustment items (STATIC and SIZE of vertical and horizontal lines, etc.) for each GH and GV, and adjust to roughly eliminate distortion. (For GV, peripheral pin distortion adjustment is necessary.)

Press the DOT key three times to enter OFFSET CONVER. MODE 3.

Press the SCREEN mode key and proceed with the adjustment for each screen mode.

The cross-hatch signal is generated inside the unit, and is automatically displayed in OFFSET CONVER. mode and MANUAL CONVERGENCE mode. You can turn on and off the cross-hatch signal with the YELLOW key.

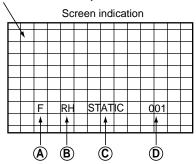

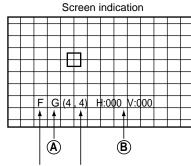

(A)

#### Screen mode:

F : FULL

Z : ZOOM

C : CINEMA

N : NATURAL

H : FULL for HD

The Screen modes change cyclically with each press of the SCREEN mode key.

**(B)**

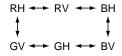

Cyclically changes with the CH+ or CH- key as follows:

(C)

Adjustment items can be selected with the numeric keys. See Table below.

# Waveforms adjustable in the coarse adjustment of the green

| Numeric Key | GH     | GV     |

|-------------|--------|--------|

| 0           | STATIC | STATIC |

| 1           | SKEW   | SKEW   |

| 6           |        | PIN    |

| 8           | SIZE   | SIZE   |

(D)

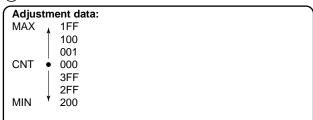

Data can be adjusted with the VOL+ and VOL- keys.

#### • Pattern for each adjustment item

**Note 1**: When the green CRT is replaced, or when the deflection yoke for the green is replaced, prior to the convergence adjustment, tune the center of the image to the center of the screen by turning the centering magnet.

Note 2: When the CONVER. AMP Assy or DIGITAL CONV. Assy is replaced, make coarse adjustment as shown in 3.3 above.

#### 3.4 Fine-adjustment of the Green

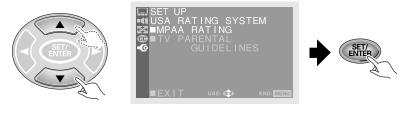

Enter MANUAL CONVERGENCE mode by pressing the SET/ENTER key, and make adjustments. Repeatedly make the coarse adjustment as shown in 3.3 if necessary. Proceed with the adjustment for each screen mode. Adjusted values for the green become the standard for the red and the blue.

#### 3.4.1

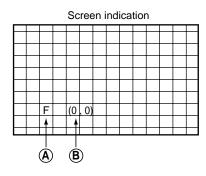

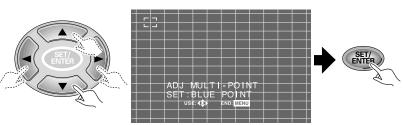

In MANUAL CONVERGENCE mode entered by pressing the SET/ENTER key, the display becomes as shown below:

**(A**)

#### Screen mode:

F : FULL

Z : ZOOM

C : CINEMA

N : NATURAL

H : FULL for HD

The Screen modes change cyclically with each press of the SCREEN mode key.

#### **(B)**

#### Coordinates where the cursor (adjustment point) is located

There are 72 adjustment points (8,9) on the coordinates for FULL, ZOOM, CINEMA, NATURAL and FULL for HD modes, but the coordinates actually used for adjustment are as follows (the coordinates outside the ranges indicated below are outside the screen, and adjustment will not have any effect on the screen):

FULL : (0, 1) to (7, 9)

ZOOM : (0, 1) to (7, 7)

CINEMA : (0, 1) to (7, 8)

NATURAL : (0, 1) to (7, 8)

HD for FULL : (0, 1) to (7, 9)

(X, Y): X=abscissa, Y=ordinate

Some coordinates may be outside the screen and invisible. The point at coordinates (0, 0) is at the upper left of the screen.

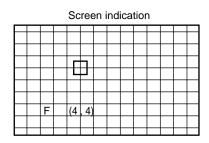

#### 3.4.2

Move the cursor to a point to be adjusted with the cursor move keys.

Note: The actual shape of the cursor is "[ ] ".

The position of the cursor in this figure is different from the actual position on the screen.

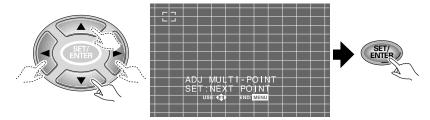

#### 3.4.3

Press the SET/ENTER key when the point to be adjusted is determined.

Screen mode Coordinates where the adjustment point is located

**(A)**

#### Color to be adjusted:

G: GREEN, R: RED, B: BLUE

To change colors, use the CH+ or CH- key.

The colors change cyclically as follows:

With CH+ :  $R \rightarrow B \rightarrow G \rightarrow R$ With CH- :  $R \rightarrow G \rightarrow B \rightarrow R$

**(B)**

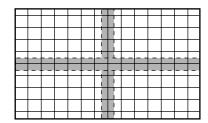

For adjustment, move the Line to the desired direction with the cursor keys.

To move the Horizontal Line upward, press the " **\Lambda** " key. (The value decreases.)

To move the Horizontal Line downward, press the " ▼" key. (The value increases.)

To move the Vertical Line to the left, press the " ◀ " key. (The value decreases.)

To move the Vertical Line to the right, press the " > " key. (The value increases.)

- To select one color, use the SEARCH key for the red, SELECT key for the green, FREEZE key for the blue. Pressing this key toggles color muting on or off.

- To mute all the colors, press the DISPLAY key. To release muting, press the SEARCH, SELECT, or FREEZE key.

- To erase the cross hatch, press the YELLOW key.

Pressing this key toggles between display of the cross hatch screen and the input screen.

- To change the brightness of the input screen, use the VOL+ or VOL- key. The brightness increases with the VOL+ key (CONTRAST +10) and decreases with the VOL- key (CONTRAST -40). (The brightness can be changed only in Fineadjustment mode. The brightness of the cross hatch screen cannot be changed.)

#### 3.4.4

When adjustment of the selected point is finished, press the SET/ENTER key, then adjust the other adjustment points by repeating 3.4.1 to 3.4.4.

#### 3.4.5

Make the adjustment for the green in each screen mode, and use the green as the standard screen for the red and the blue. To change screen modes, use the SCREEN mode key.

**Note:** Some coordinates for adjustment points are located outside the screen. Be sure not to make adjustments on those points, because adjustment of those coordinates will have little effect on the screen.

#### Adjustment Technique

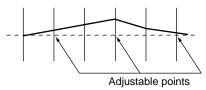

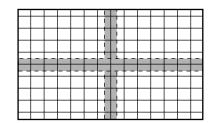

#### 1st step

Adjust so that the vertical and horizontal lines forming a cross at the center of the screen become straight. Check also the screen size and the linearity of the horizontal and vertical lines.

- See "3.3 Coarse adjustment of the green."

Adjust GH STATIC, SKEW and SIZE, and GV STATIC, SKEW, PIN and SIZE to correct the screen location, tilt, screen information volume, and peripheral pin distortion.

- See "3.4 Fine-adjustment of the green."

Fine-adjust the linearity of the vertical and horizontal lines forming a cross at the center of the screen.

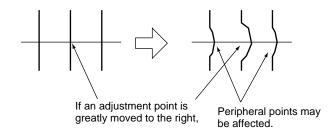

Note: In principle, only the selected point is changed in MANUAL CONVER. mode. However, as the adjusted data (amount of adjustment) increase, peripheral points may be affected. So be sure not to greatly change the adjustment data of one point, but change peripheral points at the same time. See the examples below.

In a case of an error in convergence:

Good adjustment:

Bad adjustment:

#### 2nd step

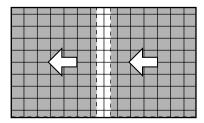

Adjust so that the vertical lines become straight, taking care to preserve proper screen information volume and the linearity. Adjust the right half of the screen first, then the left half. (See 3.4.)

Right half: Adjust from the edge toward the center. Left half: Adjust from the center toward the edge.

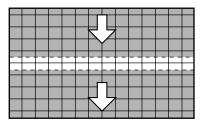

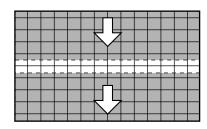

#### 3rd step

Adjust so that the horizontal lines become straight. Adjust the upper half of the screen first, then the lower half. (See 3.4.)

Upper half: Adjust from the edge toward the center. Lower half: Adjust from the center toward the edge.

#### 4th step

Repeat 2nd and 3rd steps to take total balance. Then the adjustment for the green is completed.

To return from the fine adjustment mode to the coarse adjustment mode, press the MENU key once, then the DOT key.

Note: When the MENU key is pressed to quit MANUAL CONVERGENCE mode, the display will be unstable for several seconds. This is because the adjustment data are being written to the EEPROMs, and is not a malfunction. Do not perform any operation (power on/off, or pressing keys on the remote control unit or on the main unit, etc.) during this period, because doing so may affect your adjustment data.

#### 3.5 Coarse Adjustment of the Red

After the green adjustment is completed, quit MANUAL CONVERGENCE mode by pressing the MENU or MUTING key, then press the DOT key three times to enter OFFSET CONVER. MODE 3.

Select adjustment items for RH and RV, and roughly correct distortion to converge with the green. Adjustment is required for each screen mode

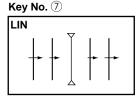

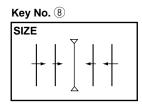

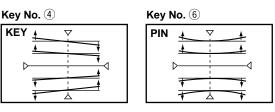

For adjustable items of the red and the blue, see the following table.

| Numeric Key | RH     | RV     | ВН     | BV     |

|-------------|--------|--------|--------|--------|

| 0           | STATIC | STATIC | STATIC | STATIC |

| 1           | SKEW   | SKEW   | SKEW   | SKEW   |

| 4           |        | KEY    |        | KEY    |

| 6           |        | PIN    |        | PIN    |

| 7           | LIN    |        | LIN    |        |

| 8           | SIZE   | SIZE   | SIZE   | SIZE   |

#### • Pattern for each adjustment item

Note 1: When the red CRT is replaced, or when the deflection yoke for the red is replaced, prior to adjustment, tune the center of the image to the center of the screen by turning the centering magnet.

Note 2: When the CONVER. AMP Assy or DIGITAL CONV. Assy is replaced, make coarse adjustment as shown in 3.5 above.

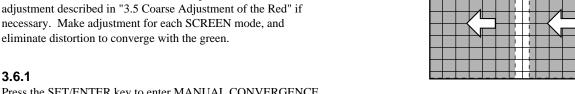

#### 3.6 Fine-adjustment of the Red

To fine-adjust the red, press the SET/ENTER key to enter MANUAL CONVERGENCE mode. Repeat the coarse adjustment described in "3.5 Coarse Adjustment of the Red" if necessary. Make adjustment for each SCREEN mode, and eliminate distortion to converge with the green.

Press the SET/ENTER key to enter MANUAL CONVERGENCE mode, and make adjustment in the same manner as with the green. First, adjust the vertical and horizontal the red lines at the center of the screen so that they converge with the green center lines.

3.6.3 Adjust the red horizontal lines so that they converge with the green horizontal lines. Proceed to adjustment of the upper half of the screen, then the lower half. Adjustment should be done from the part where convergence is greatly dislocated.

#### 3.6.2

Adjust the red vertical lines so that they converge with the green vertical lines. Proceed to adjustment of the right half of the screen, then the left half. Adjustment should be done from the part where convergence is greatly dislocated.

#### 3.6.4

Repeat the adjustments described in 3.6.2 and 3.6.3 so that all the red vertical and horizontal lines converge with the green lines. (Completion of one screen mode)

#### 3.6.5

Repeat procedures 3.6.2 through 3.6.4 for the other screen modes. (Completion of the red adjustment)

#### 3.7 Coarse Adjustment and Fine Adjustment of the Blue

Make coarse and fine-adjustments of the blue in the same manner as with the red, described in 3.5 and 3.6.

#### 3.8 Confirmation of Adjustment

After the green, red, and blue adjustments are finished, check convergence errors with the patterns for all three colors on the monitor.

Check the patterns in all SCREEN modes, and if any error in convergence is recognized, readjust convergence in MANUAL CONVER. mode.

**Note:** Be sure NOT to change the green pattern during readjustment.

#### **IMPORTANT!**

(1) When all the adjustments are completed, or when adjustment should be temporarily interrupted, adjustment data must be written to the EEPROM, in the following manner:

When all the adjustments are completed, or to interrupt adjustment, press the MENU key to quit Convergence Adjustment mode. The display will be unstable for several seconds, but this is because the data are being written to the EEPROM. Wait without doing anything until the display becomes stable, which means writing of data to the EEPROM is finished.

If the power of the TV is turned off (standby) during Convergence Adjustment mode (coarse and fine-adjustments), turn on the TV, enter FACTORY mode, and enter Convergence Adjustment mode by pressing the SET/ENTER key. Then press the MENU key. The data will be written to the EEPROM as described above.

- (2) Do NOT turn off the main power during or after convergence adjustment.

- If you do so, the adjusted data may be lost. If the data are lost, you must make all the adjustments again.

- (3) When the CENTER POINT (test cross) or MULTI-POINT (user convergence) adjustments have been made by a user, and if the unit enters FACTORY Convergence Adjustment mode (with the DOT and SET/ENTER keys), the user's adjustment data will be all cleared and returned to the factory-preset values.

Be sure NOT to enter this Convergence Adjustment mode except when a repair related to convergence or a repair that requires convergence adjustment later, is needed.

If you inadvertently enter Convergence Adjustment mode, readjust the convergence.

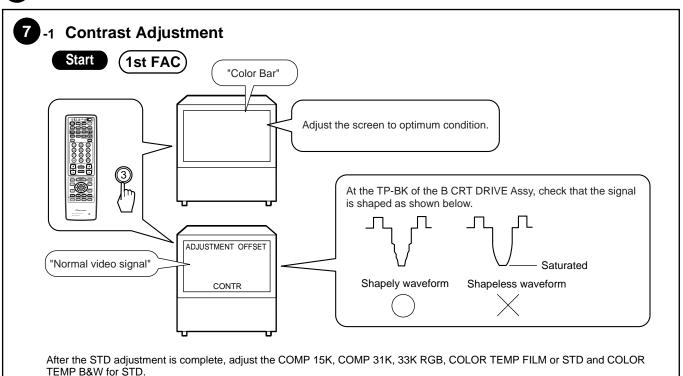

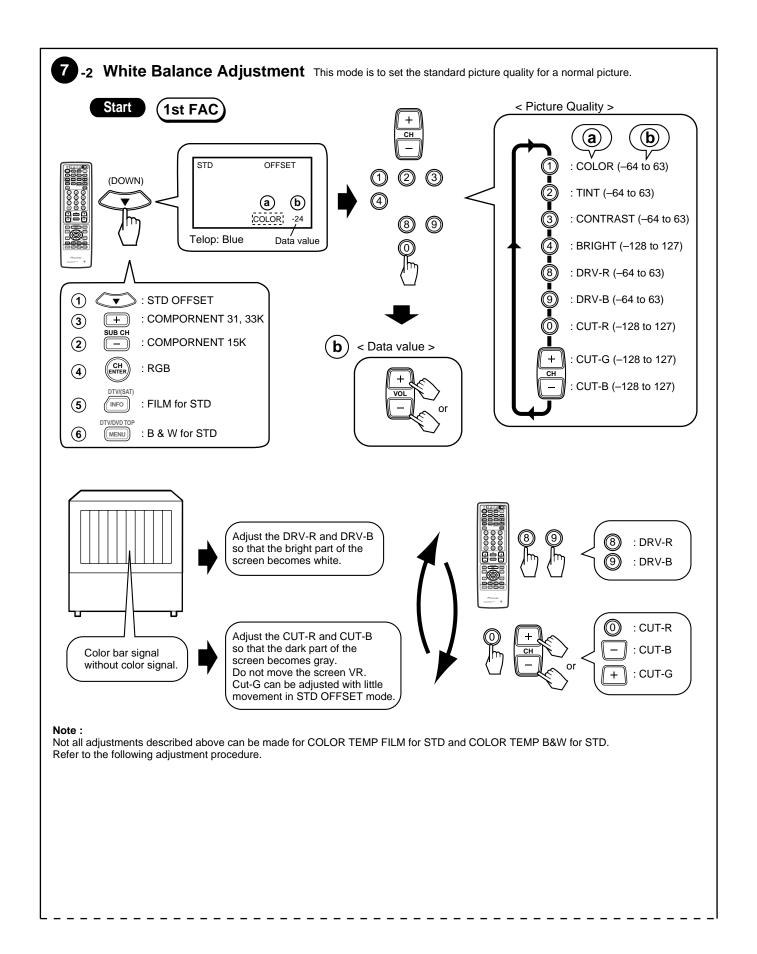

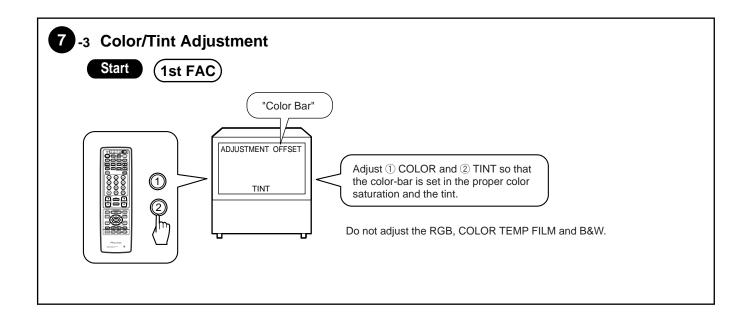

# 7 White Balance Adjustment

#### Adjustment Procedure of White Balnce

#### **OFFSET Data Table**

| COLOR   |            | Without RGB Input |      |                               |            |           |           |      |      | RGB Input |     |  |  |

|---------|------------|-------------------|------|-------------------------------|------------|-----------|-----------|------|------|-----------|-----|--|--|

| TEMP    | STD        | NEWS              | LIVE | FILM STD                      | FILM MOVIE | B&W STD   | B&W MOVIE | NEWS | LIVE | FILM      | B&W |  |  |

| Setting |            | J                 | K    | L                             | М          | V         | X         | β    | γ    | Υ         | Ζ   |  |  |

| User    | MOVIE      |                   |      | GAME                          |            |           |           |      |      |           |     |  |  |

| Mode    | Е          |                   | F    |                               |            |           |           |      |      |           |     |  |  |

|         | TV COMF    |                   | COMP | ORNENT 15K COMPORNENT 31K 33K |            | T 31K 33K | RGB       |      |      |           |     |  |  |

| Input   |            | В                 |      | С                             | D          |           | Т         |      |      |           |     |  |  |

| Signal  | STD OFFSET |                   |      |                               |            |           |           |      |      |           |     |  |  |

|         |            |                   |      |                               |            | Α         |           |      |      |           |     |  |  |

Adjustments are required for A, C, D, T, L, and V in the table above. Data in other parts are fixed. (I="0") Proceed with the adjustments in the following order:

| Adjustment (1) STD OFFSET (2) COMPONENT 15K (3) COMPONENT 31, 33K (4) RGB (5) FILM for STD | SUB CH+<br>CH ENTER<br>INFO | A+L | Picture quality data on the screen Adjustment of all standard picture qualities Adjustment of C Adjustment of D Adjustment of L Adjustment of L | table.  Do NOT change other data.  Other data are adjusted in factory shipment by Fix data of the following |

|--------------------------------------------------------------------------------------------|-----------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| (6) B&W for STD                                                                            | DTV MENU                    |     | Adjustment of V                                                                                                                                 | table . (refer to page 215.)                                                                                |

- First, perform "(1) STD OFFSET", then perform adjustments (2), (3) and (4) so that the same picture quality (color temperature) as achieved in (1) is obtained.

- In adjustment (5), make the whole picture more reddish than in (1), and in adjustment (6), make it more reddish.

- When readjusting, once "(1) STD OFFSET" is adjusted, the data for other input signals (component, etc.) revert to the factory-preset values, in principle.

- After the adjustment of STD OFFSET is completed, check other picture quality modes by switching color temperatures and signals.

It is OK if picture quality does not deviate greatly when input signal is changed (composite, component 15K, etc.).

Furthermore, it is OK if color temperature changes when color remperarure is changed.

With this model, five color temperature switching modes are provided. In FILM and B&W modes, a white part appears to be reddish in general because of their color temperature settings.

#### **OFFSET DATA (VIDEO)**

ADJ :Adjustment item

The numerical value is shipping a set value in the factory.

A set value is data of 1999.11 present provinces.

|    | · '               |               |                        |     |             |              |              |                        |     |

|----|-------------------|---------------|------------------------|-----|-------------|--------------|--------------|------------------------|-----|

| ΡĮ | DIRECT KEY        |               |                        |     | DIRECT KEY  |              |              |                        |     |

|    | OFFSET MODE MODEL |               |                        |     | OFFSET MODE |              | MODEL        |                        |     |

|    | KEY ADJ NAME      |               | PRO-610HD<br>PRO-510HD |     |             | KEY ADJ NAME |              | PRO-610HD<br>PRO-510HD |     |

| D  | OWN               |               |                        |     | В           | LUE (c       | yclically)   |                        |     |

|    | STD               | OFFSET A      |                        |     | $\  \ $     | MOVI         | E OFFSET E   |                        |     |

|    | 1                 | COLOR         | ADJ                    | ADJ |             | 1            | COLOR        | -11                    | -30 |

|    | 2                 | TINT          | ADJ                    | ADJ |             | 2            | TINT         | -13                    | -11 |

|    | 3                 | CONTRAST      | ADJ                    | ADJ |             | 3            | CONTRAST     | -27                    | -14 |

|    | 4                 | BRIGHT        | ADJ                    | ADJ |             | 4            | BRIGHT       | 0                      | 0   |

|    | 5                 | SHARPNESS     | 0                      | 0   |             | 5            | SHARPNESS    | -20                    | -20 |

|    | 6                 | DETAIL        | -50                    | -15 |             | 6            | DETAIL       | 30                     | 30  |

|    | 7                 | S. V. M       | 0                      | 0   |             | 8            | R DRV        | 1                      | -2  |

|    | 8                 | R DRV         | ADJ                    | ADJ |             | 9            | B DRV        | 4                      | 6   |

|    | 9                 | B DRV         | ADJ                    | ADJ |             | 0            | R CUT        | <del>-</del> 5         | 8   |

|    |                   |               |                        |     |             | _            |              |                        |     |

|    | 0                 | R CUT         | ADJ                    | ADJ |             | CH+          | G CUT        | -3                     | 5   |

|    | CH+               | G CUT         | ADJ                    | ADJ | II ⊢        | CH-          | B CUT        | -3                     | 4   |

| Ц. | CH-               | B CUT         | ADJ                    | ADJ |             |              | E OFFSET F   | _                      |     |

| ၂  | JB CH             |               | _                      |     |             | 1            | COLOR        | 0                      | 0   |

|    |                   |               | С                      |     |             | 2            | TINT         | 0                      | 0   |

|    | 1                 | COLOR         | ADJ                    | ADJ |             | 3            | CONTRAST     | -43                    | -28 |

|    | 2                 | TINT          | ADJ                    | ADJ |             | 4            | BRIGHT       | 0                      | 0   |

|    | 3                 | CONTRAST      | ADJ                    | ADJ |             | 5            | SHARPNESS    | -35                    | -35 |

|    | 4                 | BRIGHT        | 0                      | 0   |             | 6            | DETAIL       | 0                      | 0   |

|    | 5                 | SHARPNESS     | 0                      | 0   |             | 8            | R DRV        | 0                      | 3   |

|    | 6                 | DETAIL        | 0                      | 0   |             | 9            | B DRV        | 8                      | 7   |

|    | 7                 | S. V. M       | 0                      | 0   |             | 0            | R CUT        | 4                      | 13  |

|    | 8                 | R DRV         | ADJ                    | ADJ |             | CH+          | G CUT        | 7                      | 13  |

|    | 9                 | B DRV         | ADJ                    | ADJ |             | CH-          | B CUT        | 3                      | 11  |

|    | 0                 | R CUT         | ADJ                    | ADJ | c           | H ENT        |              |                        |     |

|    | CH+ G CUT ADJ ADJ |               |                        | [   |             | OFFSET T     |              |                        |     |

|    | CH-               | B CUT         | ADJ                    | ADJ |             | 3            | CONTRAST     | ADJ                    | ADJ |

| H  | JB CH             |               |                        | AD3 |             | 4            | BRIGHT       | ADJ                    | ADJ |

| 30 |                   |               | V D                    |     |             |              | R DRV        | ADJ                    | ADJ |

|    |                   | PONENT 31, 33 |                        | 401 |             | 8            |              |                        |     |

|    | 1                 | COLOR         | ADJ                    | ADJ |             | 9            | B DRV        | ADJ                    | ADJ |

|    | 2                 | TINT          | ADJ                    | ADJ |             | 0            | R CUT        | ADJ                    | ADJ |

|    | 3                 | CONTRAST      | ADJ                    | ADJ |             | CH+          | G CUT        | ADJ                    | ADJ |

|    | 4                 | BRIGHT        | 0                      | 0   | Щ           | CH-          | B CUT        | ADJ                    | ADJ |

|    | 5                 | SHARPNESS     | -20                    | -20 |             | IFO          |              |                        |     |

|    | 6                 | DETAIL        | 92                     | 127 |             |              | OR TEMP FILM | 1                      | L   |

|    | 7                 | S. V. M       | 0                      | 0   |             | 3            | CONTRAST     | ADJ                    | ADJ |

|    | 8                 | R DRV         | ADJ                    | ADJ |             | 8            | R DRV        | ADJ                    | ADJ |

|    | 9                 | B DRV         | ADJ                    | ADJ |             | 9            | B DRV        | ADJ                    | ADJ |

|    | 0                 | R CUT         | ADJ                    | ADJ |             | 0            | R CUT        | ADJ                    | ADJ |

|    | CH+               | G CUT         | ADJ                    | ADJ |             |              | G CUT        | ADJ                    | ADJ |

|    | CH-               | B CUT         | ADJ                    | ADJ |             | CH-          | B CUT        | ADJ                    | ADJ |

| RI | ED                |               |                        |     | D.          | TV MEI       |              |                        |     |

| ΙĒ |                   | FFSET B       |                        |     | ΙŢ          |              | OR TEMP B&W  | for STD                | V   |

| П  | 1                 | COLOR         | -10                    | -10 |             | 3            | CONTRAST     | ADJ                    | ADJ |

|    | 2                 | TINT          | 0                      | 0   |             | 8            | R DRV        | ADJ                    | ADJ |

|    | 3                 | CONTRAST      | 0                      | 0   |             | 9            | B DRV        | ADJ                    | ADJ |

|    | 4                 | BRIGHT        | 0                      | 0   |             | 0            | R CUT        | ADJ                    | ADJ |

|    | 5                 |               | 0                      |     |             |              | G CUT        |                        |     |

| Щ  | ၂ ၁               | SHARPNESS     | U                      | 0   |             | CH+<br>CH-   |              | ADJ                    | ADJ |

|    |                   |               |                        |     | Ш           | СП-          | B CUT        | ADJ                    | ADJ |

| DI       | DIRECT KEY                |                |            |            |  |  |  |  |

|----------|---------------------------|----------------|------------|------------|--|--|--|--|

| Г        | OFFSET MODE MODEL         |                |            |            |  |  |  |  |

|          | OI F3                     | LI WODE        |            |            |  |  |  |  |

|          | KEY                       | ADJ NAME       |            | SD-582HD5  |  |  |  |  |

|          |                           | 7.50           | PRO-510HD  | SD-532HD5  |  |  |  |  |

| G        | REEN                      | (cyclically)   |            |            |  |  |  |  |

| Г        |                           |                |            |            |  |  |  |  |

|          |                           |                |            | J          |  |  |  |  |

|          | 3                         | CONTRAST       | -6         | -6         |  |  |  |  |

|          | 8                         | R DRV          | -1         | -1         |  |  |  |  |

|          | 9                         | B DRV          | 16         | 16         |  |  |  |  |

|          | 0                         | R CUT          | 3          | 3          |  |  |  |  |

|          | CH+                       | G CUT          | 3          | 3          |  |  |  |  |

|          | CH-                       | B CUT          | 1          | 1          |  |  |  |  |

| $\vdash$ |                           |                |            | · ·        |  |  |  |  |

|          |                           | OR TEMP LIVE f |            | K          |  |  |  |  |

|          | 3                         | CONTRAST       | -1         | -1         |  |  |  |  |

|          | 8                         | R DRV          | <b>–</b> 5 | <b>-</b> 5 |  |  |  |  |

|          | 9                         | B DRV          | 7          | 7          |  |  |  |  |

|          | 0                         | R CUT          | 2          | 2          |  |  |  |  |

|          | CH+                       | G CUT          | 3          | 3          |  |  |  |  |

|          | CH-                       | B CUT          | 1          | 1          |  |  |  |  |

| $\vdash$ |                           |                |            |            |  |  |  |  |

|          |                           | OR TEMP FILM   |            |            |  |  |  |  |

|          | 3                         | CONTRAST       | 0          | 0          |  |  |  |  |

|          | 8                         | R DRV          | 9          | 1          |  |  |  |  |

|          | 9                         | B DRV          | -10        | -15        |  |  |  |  |

|          | 0                         | R CUT          | -1         | 0          |  |  |  |  |

|          | CH+                       | G CUT          | 0          | 0          |  |  |  |  |

|          | CH-                       | B CUT          | 1          | 0          |  |  |  |  |

| H        |                           |                |            |            |  |  |  |  |

|          |                           | OR TEMP B&W    |            |            |  |  |  |  |

|          | 3                         | CONTRAST       | -1         | 0          |  |  |  |  |

|          | 8                         | R DRV          | 15         | 6          |  |  |  |  |

|          | 9                         | B DRV          | -17        | -22        |  |  |  |  |

|          | 0                         | R CUT          | 1          | 1          |  |  |  |  |

|          | CH+                       | G CUT          | 2          | 2          |  |  |  |  |

|          | CH-                       | B CUT          | 3          | 1          |  |  |  |  |

| G        |                           | (cyclically)   | _          |            |  |  |  |  |

| ĭ        |                           | OR TEMP NEWS   | for PCP    | β          |  |  |  |  |

|          |                           |                |            |            |  |  |  |  |

|          | 3                         | CONTRAST       | -6         | <u>-6</u>  |  |  |  |  |

|          | 4                         | BRIGHT         | 0          | 0          |  |  |  |  |

|          | 8                         | R DRV          | -1         | -1         |  |  |  |  |

|          | 9                         | B DRV          | 16         | 16         |  |  |  |  |

|          | 0                         | R CUT          | 3          | 3          |  |  |  |  |

|          | CH+                       | G CUT          | 3          | 3          |  |  |  |  |

|          | CH-                       | B CUT          | 1          | 1          |  |  |  |  |

| F        | COLOR TEMP LIVE for RGB γ |                |            |            |  |  |  |  |

|          |                           | CONTRAST       |            | -1         |  |  |  |  |

|          |                           |                |            | -          |  |  |  |  |

|          | 4                         | BRIGHT         | 0          | 0          |  |  |  |  |

|          | 8                         | R DRV          | <b>-</b> 5 | -5         |  |  |  |  |

|          | 9                         | B DRV          | 7          | 7          |  |  |  |  |

|          | 0                         | R CUT          | 2          | 2          |  |  |  |  |

|          | CH+                       | G CUT          | 3          | 3          |  |  |  |  |

|          | CH-                       | B CUT          | 1          | 1          |  |  |  |  |

| $\vdash$ |                           | OR TEMP FILM 1 | or RGB     | Υ          |  |  |  |  |

|          | 3                         | CONTRAST       | <u>-1</u>  | -1         |  |  |  |  |

|          | 4                         | BRIGHT         | 0          | 0          |  |  |  |  |

|          |                           | R DRV          | 14         | 14         |  |  |  |  |

|          | 8                         |                |            | -10        |  |  |  |  |

|          | 9                         | B DRV          | -10        | _          |  |  |  |  |

|          | 0                         | R CUT          | 1          | 1          |  |  |  |  |

|          | CH+                       | G CUT          | 3          | 3          |  |  |  |  |

| L        | CH-                       | B CUT          | 4          | 4          |  |  |  |  |

|          | COL                       | OR TEMP B&W    | or RGB     | Z          |  |  |  |  |

|          | 3                         | CONTRAST       | -1         | -1         |  |  |  |  |

|          | 4                         | BRIGHT         | 0          | 0          |  |  |  |  |

|          | 8                         | R DRV          | 18         | 18         |  |  |  |  |

|          | 9                         | B DRV          | -17        | -17        |  |  |  |  |

|          | 0                         | R CUT          | -1         | -1         |  |  |  |  |

|          |                           |                | 2          | 2          |  |  |  |  |

|          | (`L                       |                |            | _          |  |  |  |  |

|          | CH-                       | G CUT          |            |            |  |  |  |  |

|          | CH+                       | B CUT          | 4          | 4          |  |  |  |  |

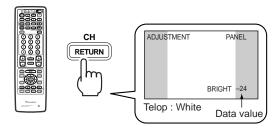

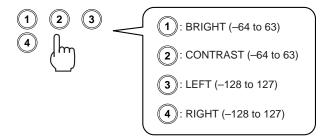

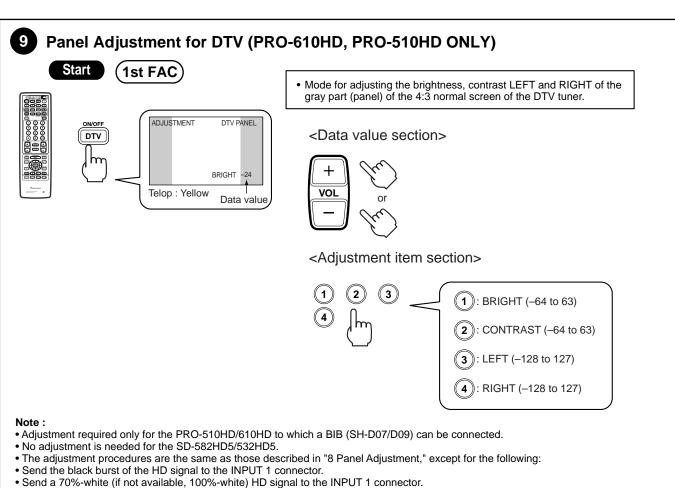

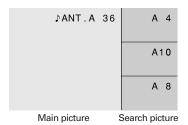

Mode for adjusting the brightness, contrast LEFT and RIGHT of the gray part (panel) of the 4:3 normal screen.

<Data value section>

<Adjustment item section>

#### **Procedures**

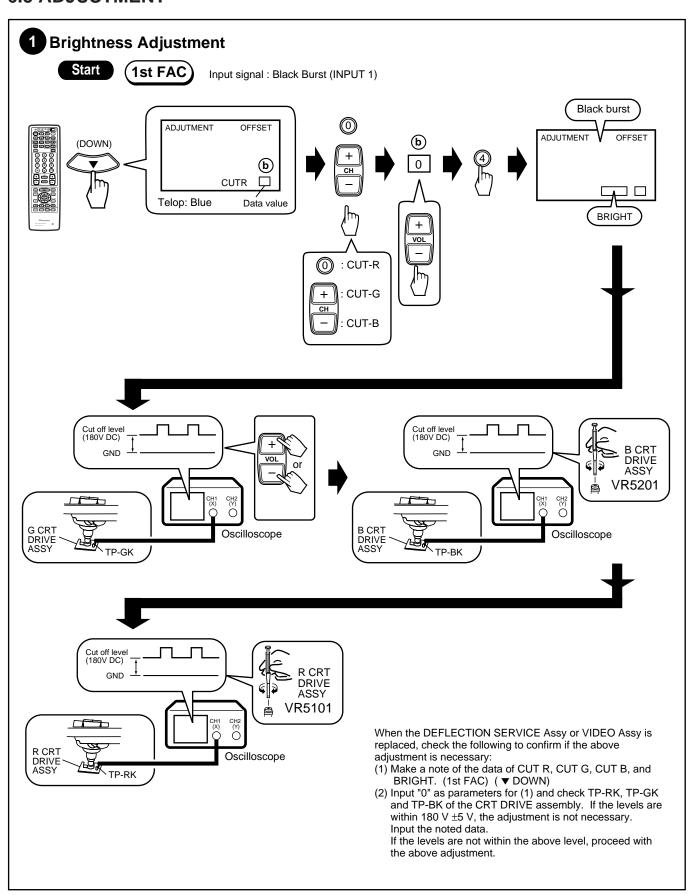

- ① Send the black-burst signal to the INPUT 1 connector.

- Enter Adjustment mode by following the procedures described above.

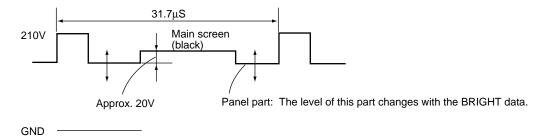

- With BRIGHT, adjust the gray part (panel) of the screen.

By observing TP5151 of the GREEN CRT DRIVE assembly with the oscilloscope, adjust the brightness level which is low by 20V from Black level of the main screen.

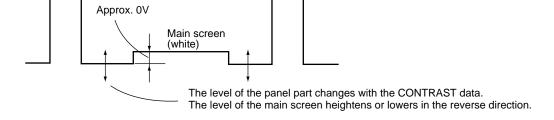

③ Switch the input signal to a 100%-white signal. Adjust the panel part and the main screen with CONTRAST. Observe the same site as described in Step ② above, and adjust the amplitude of the luminosity.

Adjust so that the level of the luminosity of the panel and that of the main screen become the same.

• As for the size adjustment, adjust so that the panel size becomes the same as that adjusted in "8 Panel Adjustment."

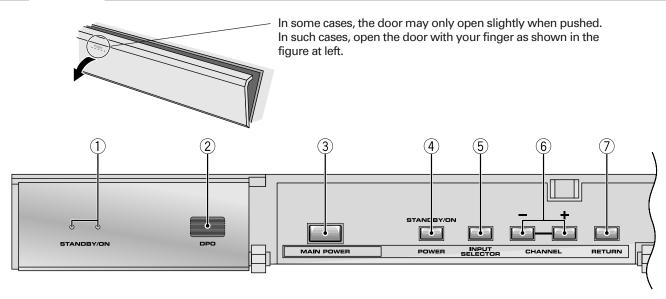

# 7. GENERAL INFORMATION

#### 7.1 DIAGNOSIS

#### 7.1.1 DIAGNOSIS METHOD

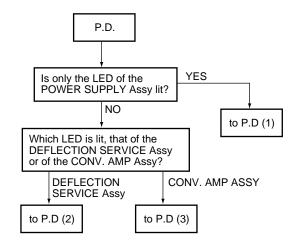

Various protection circuits are provided for this unit. When these protection circuits are activated, the power of the unit is shut down (P.D.: Power Down).

The defective parts can be easily diagnosed by observing the LEDs inside the following assemblies.

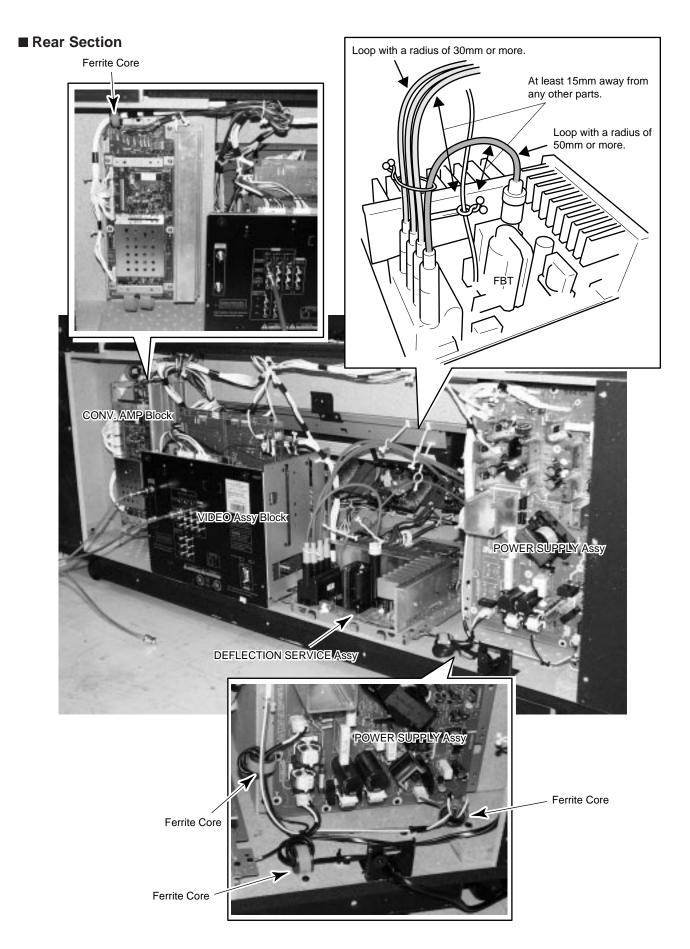

1. POWER SUPPLY Assy

For models PRO-610HD/510HD : D915 in the AWV1795 For models SD-582HD5/532HD5 : D915 in the AWV1808

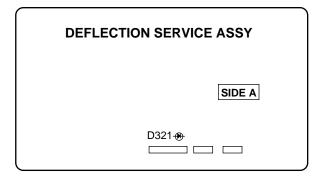

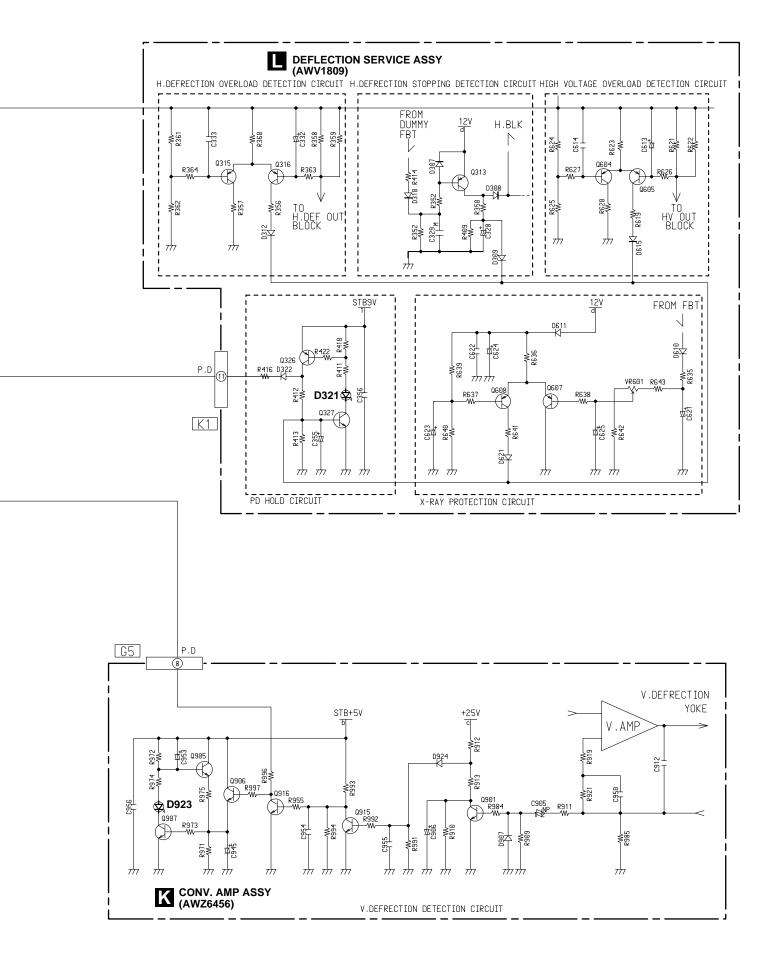

2. DEFLECTION SERVICE Assy

Common to all models : D321 in the AWV1796 For service assembly : D321 in the AWV1809

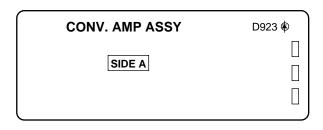

3. CONV. AMP Assy

Common to all models : D923 in the AWZ6456

# POWER SUPPLY ASSY SIDE A

LED points

#### How to diagnose a failure

The D915 LED of the POWER SUPPLY Assy always lights up when the power is turned off because of the protection circuits (P.D.).

#### 1. P.D. (1)

Failure in the POWER SUPPLY Assy and the AUDIO Assy.

There are four main possibilities:

- 1. Abnormality in the regulator of the heater

- 2. Blown fuse(s) in secondary

- 3. Abnormality in RELAY (RY102)

- 4. Abnormality in AUDIO OUTPUT

| Status           | Causes                                      | Check Items                                                                                        | Probable Defective Parts                   |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------|

| D223<br>ANODE Hi | Abnormality in the regulator for the heater | The voltage of HT- at TP205 is NOT approx. 19 V, and that of the HT+ at TP204 is NOT approx. 26 V. | Q201, R202, D210, D209                     |

| D207             |                                             | The voltage HT+ (approx. 26 V) at TP204 is NOT supplied.                                           | CONV. AMP Assy and DEFLECTION SERVICE Assy |

| ANODE Hi         | Blown fuse(s)                               | The voltage (approx. 35 V) at TP203 is NOT supplied.                                               | AUDIO Assy                                 |

|                  |                                             | The voltage (approx. 11 V) at TP209 is NOT supplied.                                               | VIDEO Assy                                 |

| D911<br>ANODE Hi | Abnormality in RELAY                        | The RELAY signal is NOT high (ON) at TP904.                                                        | SIGNAL Assy                                |

|                  |                                             | P.D. even if the RELAY signal is high (ON) at TP904.                                               | Q904, Q905 RY102, R102                     |

| D203<br>ANODE Hi | Abnormality in AUDIO OUTPUT                 | The SP line (CN5611) is disconnected.                                                              | Connect the SP line.                       |

|                  |                                             | The voltage at the negative electrode of the C5616 and C5617 is 5.2 V or more.                     | C5616, C5617 (VIDEO Assy)                  |

**Note:** The anode of the diode is high only for a short time after the power is turned on until the protection circuits are activated (P.D.) The LEDs are lit by the HOLD circuit.

In a case when the power cannot be on with no LED lit, check the following:

- 1. Check if the FU101 fuse in the POWER SUPPLY Assy is blown.

- 2. Disconnect and check connector E1 (CN201) to see whether STB 5 V is supplied.

If STB 5 V is supplied, replace the SIGNAL Assy. If STB 5 V is NOT supplied, replace the POWER SUPPLY Assy.

- 3. Disconnect and check connector E1 (CN201) to see whether AC CLK is supplied.

If AC CLK is supplied, replace the SIGNAL Assy. If AC CLK is NOT supplied, replace the POWER SUPPLY Assy.

#### 2. P.D. (2)

Failure in the DEFLECTION SERVICE Assy.

There are four main possibilities:

- 1. H. deflection overload detection (1)

- 2. H. deflection stopping detection

- 3. H. deflection overload detection (2)

- 4. X-ray protection

| Status           | Causes                 | Check Items                                                                                                                                    | Probable Defective Parts                        |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| D312<br>ANODE Hi | Overload detection 1   |                                                                                                                                                | Q309, Q324 (short-circuited between C and E)    |

| D309<br>ANODE Hi | Stopping H. deflection | Is the connector of the deflection yoke plugged in?                                                                                            | Plug in the connector.                          |

|                  |                        | No H. OSC signal at TP304 (F=31.5 kHz, Duty 50%)                                                                                               | IC301, Q309                                     |

|                  |                        | No DH. BLK signal at TP305                                                                                                                     | Q309                                            |

| D615<br>ANODE Hi | Overload detection 2   |                                                                                                                                                | Q612, Q613 (short-circuited between C and E)    |

|                  |                        | About one minute after the power is turned off, disconnect the K4 connector and turn on the power. Then the power is not turned off (no P.D.). | IC5101, IC5151 and IC5201 in the CRT DRIVE Assy |

| D621<br>ANODE Hi | X-ray protection       | No change in the ABL voltage (no DC change) at Pin 12 of<br>the CN305 when a 100%-white signal is repeatedly<br>connected and disconnected     | D2224 (short-circuited)of the SUB<br>VIDEO Assy |

|                  |                        |                                                                                                                                                | T601 (FBT) rare short                           |

**Note:** The anode of the diode is high only for a short time after the power is turned on until the protection circuits are activated (P.D.) The LEDs are lit by the HOLD circuit.

Note that the power may be shut down when the voltages 130 V, 25 V, and 12 V from the POWER SUPPLY Assy are not supplied because the DEFLECTION SERVICE Assy is powered by the POWER SUPPLY Assy.

When overload detection mechanisms 1 and 2 are activated, the 130 V line is short-circuited. If the power switch is set to ON again in this condition, there may be a case where the power cannot be turned on, with just a whining sound, and where only the D915 LED in the POWER SUPPLY Assy is lit. If this happens, first replace only the DEFLECTION SERVICE Assy, disconnect the AC cord from the AC outlet or turn the main power switch OFF, and wait for five minutes. Then, turn on the power again. If the condition is ameliorated, only the DEFLECTION SERVICE Assy is defective. If the same symptom occurs, replace the POWER SUPPLY Assy. In the latter case, the DEFLECTION SERVICE Assy may not be defective.

Be sure to check the fuses in the POWER SUPPLY Assy because one or more may be blown as a result of short-circuiting of the load circuit of the DEFLECTION SERVICE Assy.

#### 3. P.D. (3)

Failure in the CONV. AMP Assy The following reason may be suspected:

| 4  | <b>T</b> 7 | 1 (1       |          | 4         |

|----|------------|------------|----------|-----------|

|    | v          | deflection | stonning | detection |

| 1. | ٠.         | acricetion | Stopping | actection |

| Status                 | Causes Check Items                                                                                                                                                                                                                                                                                                                   |                                                                              | Probable Defective Parts     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|

| D923, P.D.<br>LED, lit | CONV. Assy are plugged in.  Check that the connector (H4) from the POWER SUPPLY Assy is plugged in to the DIGITAL CON' Assy.  Check that the connector (H3) from the DEFLECTION SERVICE Assy is plugged in to the DIGITAL CONV. Assy.  Abnormality in V. BLK 2 waveform that is output from Pin 6 of the CN1653 in the DIGITAL CONV. | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                        | Plug in the connectors.      |

|                        |                                                                                                                                                                                                                                                                                                                                      | Check that the connectors (G4, G5) of the DIGITAL CONV. Assy are plugged in. | Plug in the connectors.      |

|                        |                                                                                                                                                                                                                                                                                                                                      | SUPPLY Assy is plugged in to the DIGITAL CONV.                               | Plug in the connectors.      |

|                        |                                                                                                                                                                                                                                                                                                                                      | DEFLECTION SERVICE Assy is plugged in to the                                 | Plug in the connectors.      |

|                        |                                                                                                                                                                                                                                                                                                                                      |                                                                              | IC4802 in the SUB VIDEO Assy |

|                        |                                                                                                                                                                                                                                                                                                                                      | IC301 in the DEFLECTION SERVICE<br>Assy                                      |                              |

|                        |                                                                                                                                                                                                                                                                                                                                      | No waveform is output from Pin 1 of the CN902.                               | Q913, Q914                   |

**Note:** The anode of the diode is high only for a short time after the power is turned on until the protection circuits are activated (P.D.) The LEDs are lit by the HOLD circuit.

Be sure to check the fuses in the POWER SUPPLY Assy because one or more may be blown as a result of short-circuiting of the load circuit of the CONV. AMP Assy. See the table below.

Note that the power may be shut down when the voltages 25 V, -20 V, +5 V and -5 V from the POWER SUPPLY Assy are not supplied because the CONV. AMP and DIGITAL CONVER. Assys are powered by the POWER SUPPLY Assy.

#### If the FU202 and FU204 fuses are blown, see the following table:

| Causes                              | Check Items                                                                                                                                     | Probable Defective Parts |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Too high loading on the CONVER. AMP | Check that waveform signals are output from Pin 3 and Pin 5 of the CN901, CN902 and CN903, and that the DC element is not added to the signals. | IC901, IC903             |

| CONVER. MUTING not activated        | Check that the electric potential of Pin 3 and Pin 4 of IC901 and IC903 are at the same level when the power is turned on.                      | Q904, Q918               |

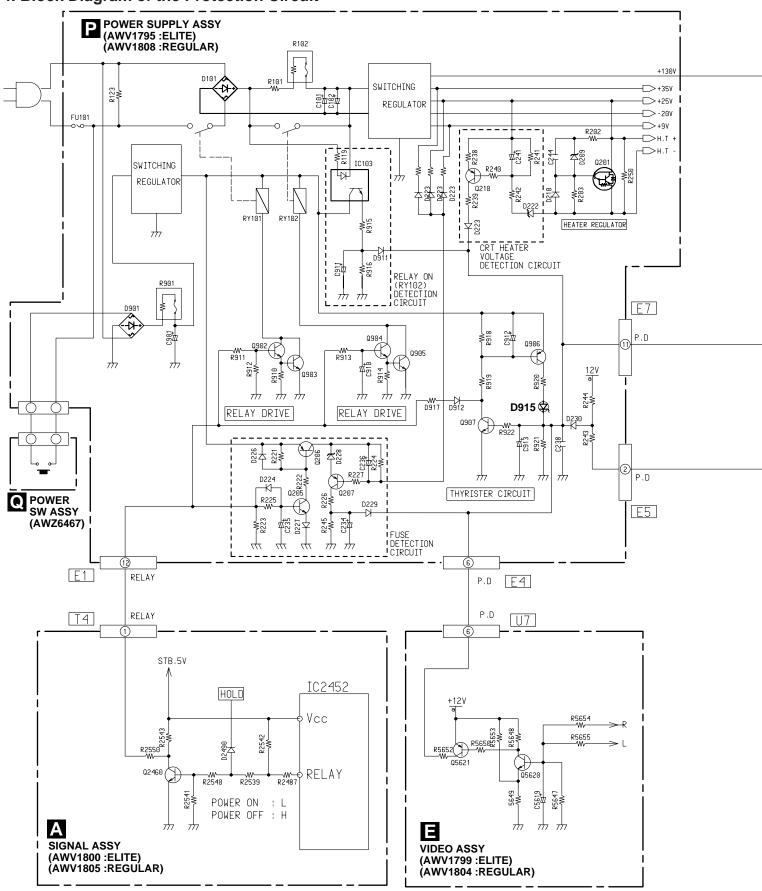

#### 4. Block Diagram of the Protection Circuit

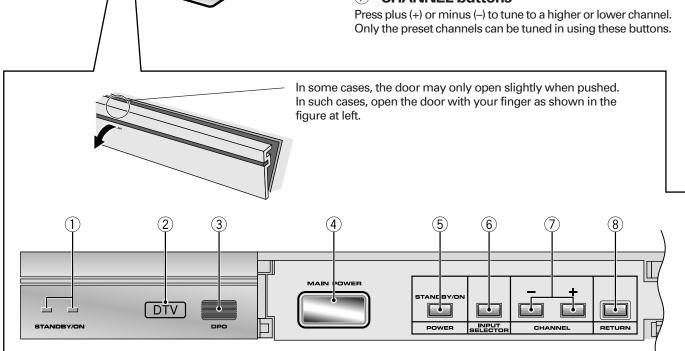

#### 7.1.2 DISASSEMBLY

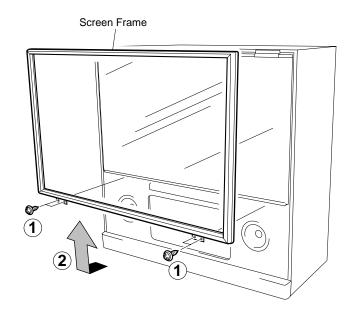

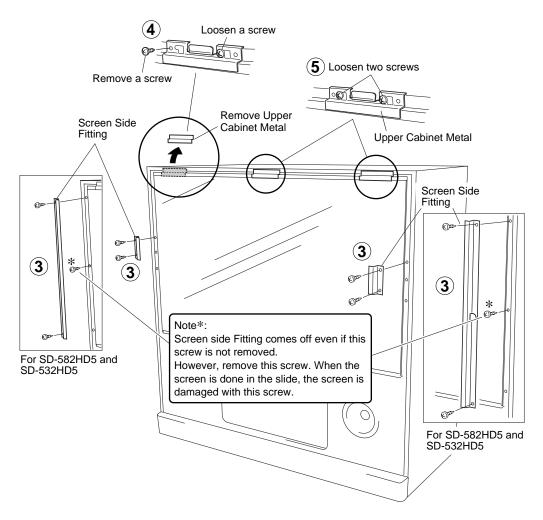

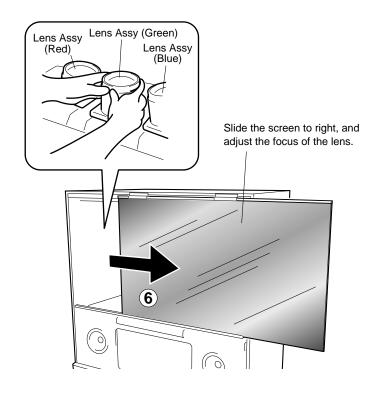

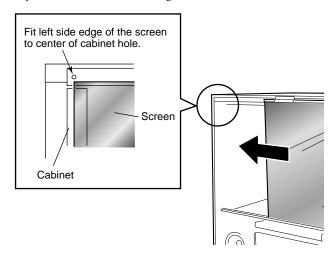

■ How to remove the screen (for adjusting Lens assemblies)

#### Notes:

To assemble the screen, perform the above procedures in reverse order.

After assembling it, verify that the right and left sides of the screen are positioned as shown in the figure.

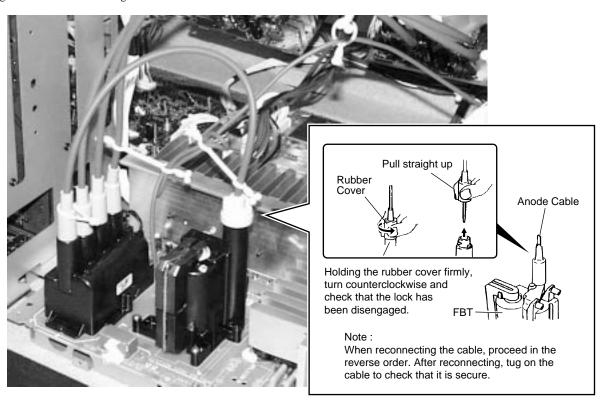

#### **■** Disconnect the Anode Cable

#### WARNING:

Before disconnect the anode cable, turn off the power, unplug the AC plug and let the unit discharge for more than 1 minut.

# 7.1.3 WIRING DIAGRAM

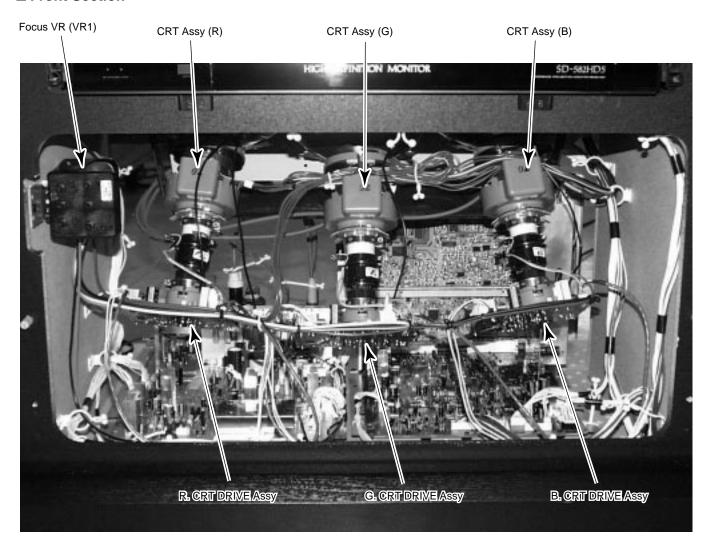

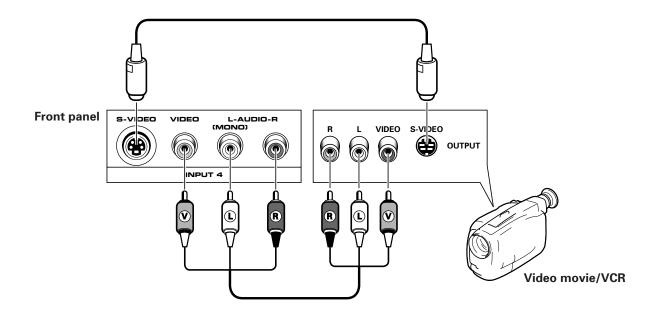

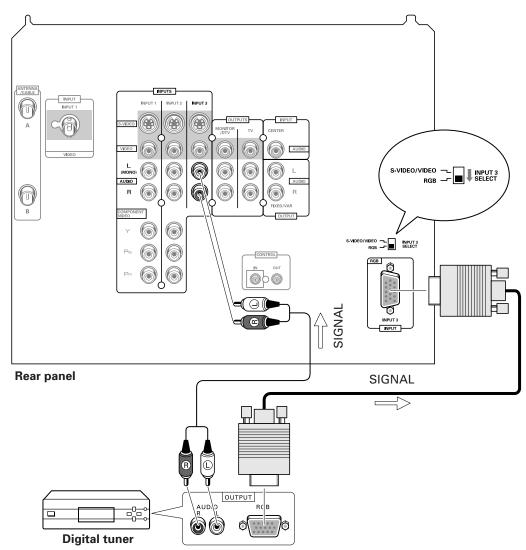

#### **■** Front Section

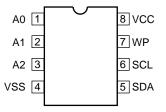

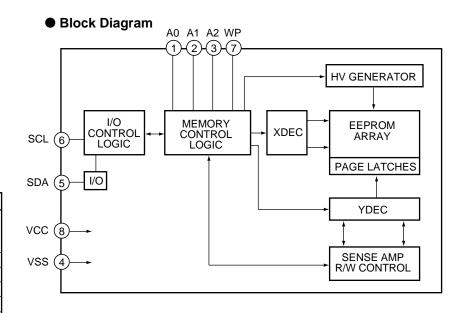

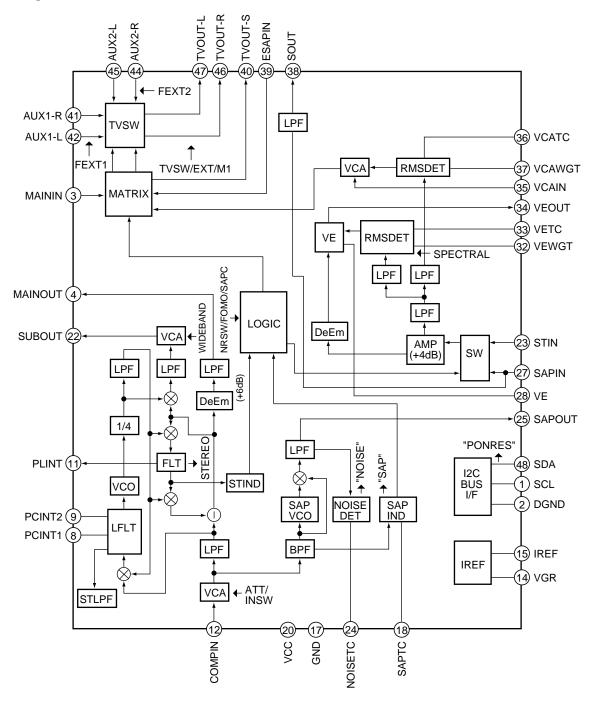

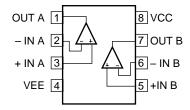

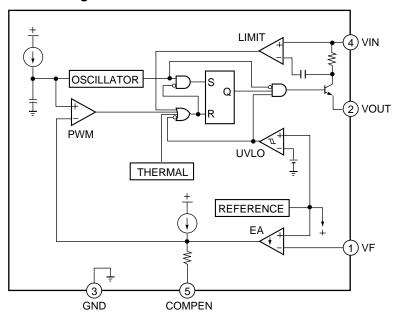

#### 7.2 IC

• The information shown in the list is basic information and may not correspond exactly to that shown in the schematic diagrams.

#### List of IC

CXD2303AQ, MB40958PFQ, CXA3106Q, PE5066A, PE5067A, EM636327Q-8, PD3420AB, SAA4990H, CD74HCT4046AM, SAA4955TJ, SAA4997H-K, 24LC128(I)P, 24LC08B(I)P, CM0006C1F, 24LC32A(I)P, ML6420CS-3, CXA2094Q, CM0010AF, TK15420M, MC33167TV

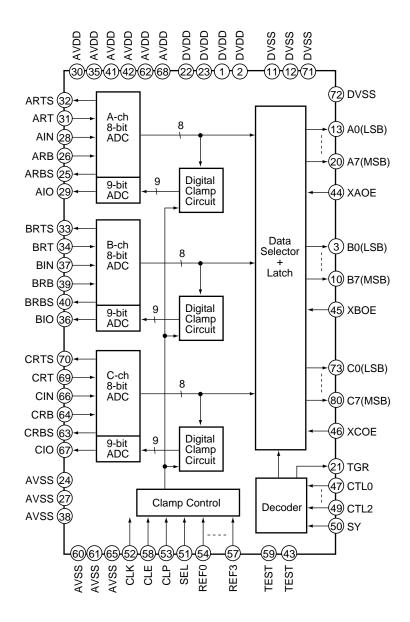

#### ■ CXD2303AQ (SUB VIDEO SERVICE ASSY: IC3203) (PRO-610HD, PRO-510HD ONLY)

• Video A/D Converter

#### • Block Diagram

| No. | Pin Name | I/O | Pin Function                                                | No. | Pin Name | I/O | Pin Function                                                                                           |

|-----|----------|-----|-------------------------------------------------------------|-----|----------|-----|--------------------------------------------------------------------------------------------------------|

| 1   | DVDD     | _   | Digital power supply +5V or +3.3V                           | 41  | AVDD     | _   | Analog power supply +5V                                                                                |

| 2   | DVDD     | _   | Digital power supply +3v or +3.3v                           | 42  | AVDD     | ı   | Analog power supply +5 v                                                                               |

| 3   | В0       |     |                                                             | 43  | TEST     | I   | Open at normal use (built-in pull-down resistor)                                                       |

| 4   | B1       |     |                                                             | 44  | XAOE     |     | Output enable input                                                                                    |

| 5   | B2       |     | Digital output (B0: LSB, B7: MSB)                           | 45  | XBOE     | I   | L: output, H: High-impedance                                                                           |

| 6   | B3       | 0   |                                                             | 46  | XCOE     |     |                                                                                                        |

| 7   | B4       |     | 3                                                           | 47  | CTL0     |     | Decides the digital output mode                                                                        |

| 8   | B5       |     |                                                             | 48  | CTL1     | ı   | (built-in pull-down resistor)                                                                          |

| 9   | B6       |     |                                                             | 49  | CTL2     |     |                                                                                                        |

| 10  | B7       |     |                                                             | 50  | SY       | I   | Control the switching timing of the digital output mode (built-in pull-down resistor)                  |

| 11  | DVSS     | _   | Digital ground                                              | 51  | SEL      | I   | Control the polarity of CLP signal L: CLP is High, H: CLP is Low (built-in pull-down resistor)         |

| 12  | DVSS     | _   |                                                             | 52  | CLK      | _   | Clock input (built-in pull-down resistor)                                                              |

| 13  | A0       |     |                                                             | 53  | CLP      | I   | Clamp pulse input (built-in pull-down resistor)                                                        |

| 14  | A1       |     |                                                             | 54  | REF0     |     |                                                                                                        |

| 15  | A2       |     |                                                             | 55  | REF1     |     | Decides the reference data of the clamp                                                                |

| 16  | A3       |     |                                                             | 56  | REF2     | '   | circuit (built-in pull-down resistor)                                                                  |

| 17  | A4       | 0   | Digital output (A0: LSB, A7: MSB)                           | 57  | REF3     |     |                                                                                                        |

| 18  | A5       |     |                                                             | 58  | CLE      | I   | Clamp enable L: Clamp circuit is not operate , H: Clamp circuit operates (built-in pull-down resistor) |

| 19  | A6       |     |                                                             | 59  | TEST     | I   | Open at normal use (built-in pull-down resistor)                                                       |

| 20  | A7       |     |                                                             | 60  | AVSS     | _   | Analog ground                                                                                          |

| 21  | TGR      | 0   | Trigger output                                              | 61  | AVSS     | _   |                                                                                                        |

| 22  | DVDD     | _   |                                                             | 62  | AVDD     | -   | Analog power supply +5V                                                                                |

| 23  | DVDD     | _   | Digital power supply +5V or +3.3V                           | 63  | CRBS     | -   | Generates about 0.5V to CRB pin by short-circuiting to AVSS                                            |

| 24  | AVSS     | _   | Analog ground                                               | 64  | CRB      | _   | Reference voltage (Bottom)                                                                             |

| 25  | ARBS     | -   | Generates about 0.5V to ARB pin by short-circuiting to AVSS | 65  | AVSS     | _   | Analog ground                                                                                          |

| 26  | ARB      | _   | Reference voltage (Bottom)                                  | 66  | CIN      | I   | Analog input                                                                                           |

| 27  | AVSS     | _   | Analog ground                                               | 67  | CIO      | 0   | Analog output (D/A converter output pin)                                                               |

| 28  | AIN      | I   | Analog input                                                | 68  | AVDD     | _   | Analog power supply +5V                                                                                |

| 29  | AIO      | 0   | Analog output (D/A converter output pin)                    | 69  | CRT      | _   | Reference voltage (Top)                                                                                |

| 30  | AVDD     | _   | Analog power supply +5V                                     | 70  | CRTS     | -   | Generates about 2.5V to CRT pin by short-circuiting to AVDD                                            |

| 31  | ART      | _   | Reference voltage (Top)                                     | 71  | DVSS     | _   |                                                                                                        |

| 32  | ARTS     | _   | Generates about 2.5V to ART pin by short-circuiting to AVDD | 72  | DVSS     |     | Digital ground                                                                                         |

| 33  | BRTS     | _   | Generates about 2.5V to BRT pin by short-circuiting to AVDD | 73  | C0       |     |                                                                                                        |

| 34  | BRT      | _   | Reference voltage (Top)                                     | 74  | C1       |     |                                                                                                        |

| 35  | AVDD     | _   | Analog power supply +5V                                     | 75  | C2       |     |                                                                                                        |

| 36  | BIO      | 0   | Analog output (D/A converter output pin)                    | 76  | C3       | 0   | Digital output (CO: LSB, C7: MSB)                                                                      |

| 37  | BIN      | I   | Analog input                                                | 77  | C4       |     | Digital output (C0: LSB, C7: MSB)                                                                      |

| 38  | AVSS     | _   | Analog ground                                               | 78  | C5       |     |                                                                                                        |

| 39  | BRB      | _   | Reference voltage (Bottom)                                  | 79  | C6       |     |                                                                                                        |

| 40  | BRBS     | _   | Generates about 0.5V to BRB pin by short-circuiting to AVSS | 80  | C7       |     |                                                                                                        |

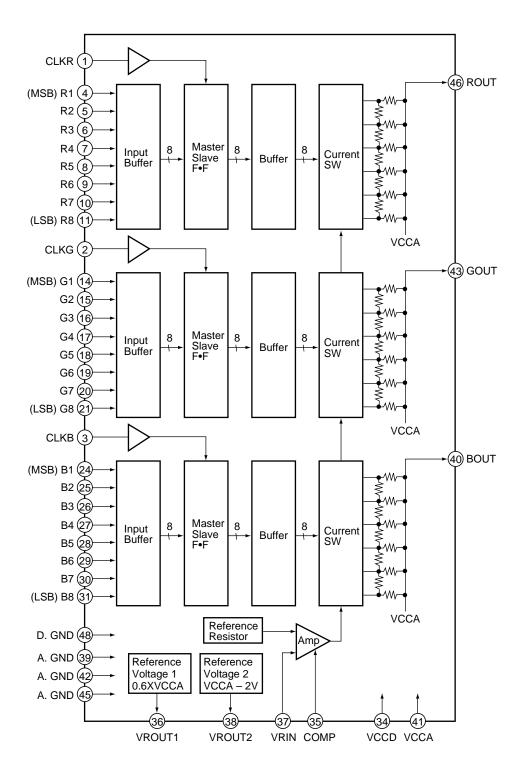

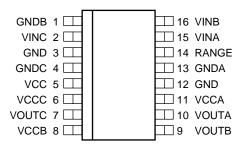

# ■ MB40958PFQ (SUB VIDEO SERVICE ASSY: IC3602) (PRO-610HD, PRO-510HD ONLY)

- D/A Converter

- Block Diagram

| No. | Pin Name | I/O | Pin Function                                                                                 |

|-----|----------|-----|----------------------------------------------------------------------------------------------|

| 1   | CLKR     | I   | R ch clock signal input                                                                      |

| 2   | CLKG     | I   | G ch clock signal input                                                                      |

| 3   | CLKB     | I   | B ch clock signal input                                                                      |

| 4   | R1       |     |                                                                                              |

| 5   | R2       |     |                                                                                              |

| 6   | R3       |     |                                                                                              |

| 7   | R4       |     | R ch data signal input (R1: MSB, R8: LSB)                                                    |

| 8   | R5       | '   | K off data signal input (KT. MOD, Ko. LOD)                                                   |

| 9   | R6       |     |                                                                                              |

| 10  | R7       |     |                                                                                              |

|     | R8       |     |                                                                                              |

| 12  | N.C.     | _   | Non connection                                                                               |

| 13  | N.C.     | _   | Non connection                                                                               |

| 14  | G1       |     |                                                                                              |

| 15  | G2       |     |                                                                                              |

| 16  | G3       |     |                                                                                              |

| 17  | G4       | 1   | G ch data signal input (G1: MSB, G8: LSB)                                                    |

| 18  | G5       | '   | o ar data signar input (O1. WOD, OC. LOD)                                                    |

| 19  | G6       |     |                                                                                              |

| 20  | G7       |     |                                                                                              |

| 21  | G8       |     |                                                                                              |

|     | N.C.     | _   | Non connection                                                                               |

| 23  | N.C.     |     | TWO COMPOSITION                                                                              |

| 24  | B1       |     |                                                                                              |

| 25  | B2       |     |                                                                                              |

|     | B3       |     |                                                                                              |

| 27  | B4       |     | B ch data signal input (B1: MSB, B8: LSB)                                                    |

| 28  | B5       | '   | b off data signal input (b 1. Mob, bo. Lob)                                                  |

| 29  | B6       |     |                                                                                              |

|     | B7       |     |                                                                                              |

|     | B8       |     |                                                                                              |

|     | N.C.     | _   | Non connection                                                                               |

| 33  | N.C.     |     |                                                                                              |

| 34  | VCCD     | _   | Digital power supply (+5V)                                                                   |

| 35  | COMP     | _   | Phase compensating capacitance pin Connect a 0.1µF capacitor between this pin and A.GND pin. |

|     | VROUT1   | 0   | Reference voltage output 1                                                                   |

|     | VRIN     | I   | Reference voltage input                                                                      |

| 38  | VROUT2   | 0   | Reference voltage output 2                                                                   |

|     | A.GND    | _   | Analog ground (0V)                                                                           |

|     | BOUT     | 0   | B ch analog signal output                                                                    |